不明白的二分频采样电路

时间:10-02

整理:3721RD

点击:

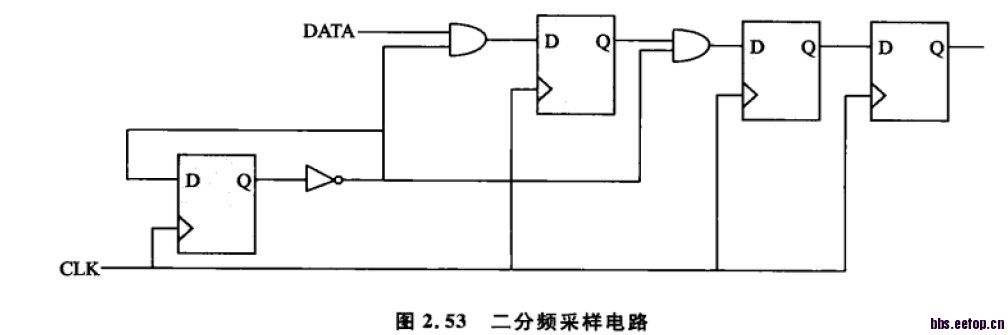

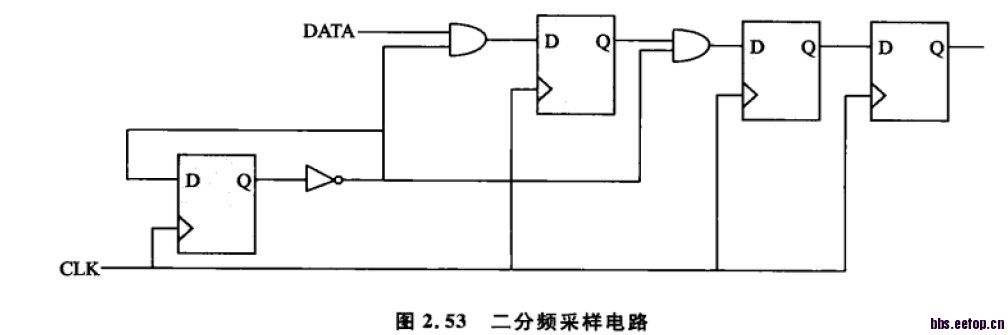

看《深入浅出玩转FPGA》这本书时看到作者给出的二分频采样电路。他是这样描述的:

“前两级采样电路都做了二分频,然后第3级使用原来时钟进行采样。它的好处在于第1级和第2级同步寄存器更多的tMET时间,将亚稳态抑制在第2级寄存器输入之前,从而保证第3级寄存器的可靠采样。虽然它在1、2级寄存器的输入端增加了一些逻辑,可能会增大TDATA,但是相比于这个采样时钟的一半降额,它的变化是可以忽略不计的。”其中DATA是异步信号。

不是很明白这样做同步处理的原理,和一般的两级同步器有什么区别。

“前两级采样电路都做了二分频,然后第3级使用原来时钟进行采样。它的好处在于第1级和第2级同步寄存器更多的tMET时间,将亚稳态抑制在第2级寄存器输入之前,从而保证第3级寄存器的可靠采样。虽然它在1、2级寄存器的输入端增加了一些逻辑,可能会增大TDATA,但是相比于这个采样时钟的一半降额,它的变化是可以忽略不计的。”其中DATA是异步信号。

不是很明白这样做同步处理的原理,和一般的两级同步器有什么区别。

我分析的结果是,这个二级采样根本什么都采样不到,永远是0,根本就是错误的。

我们集中看着两个“与门”。首先,他们有一个共同的输入,就是CLK的二分频时钟。CLK的二分频时钟有一个特性,就是一个时钟为高,那么下一个时钟就为低,这样0,1跳变的。而第一个与门和第一个与门中间有一个flop(寄存器),寄存器也有一个特性,这个时钟D为1,那么下个周期Q就是1,这个时钟D为0,那么下个周期Q就是0.

奇怪的现象来了,(这里我根本不看DATA,因为它是什么值无所谓)

1. 假设第一级的与门和寄存器采样到了1,那么下一级一定是0。因为第一级采样到1至少表明与门输入为1。表示本周期CLK二分频一定是1。(那么下周期CLK的二分频一定是0)。

2. 那么下个周期与门的输入一定为0,因为下周期,CLK的二分频一定是0.

3. 假设第一级的与门和寄存器采样到0,那么不解释,第二级一定也会采样到0.

4. 最后的结论是,第二级的寄存器一定采样到0.

综上所述,这个电路是错误的。

我本人也做过功能仿真,证明了我的推导过程。当然,也不排除我的分析和仿真有错,欢迎讨论和指正。

做了小实验,果然如你所说,输出一直为0.

明显,画一下时序就知道,图给错了。

作者吴厚航很快给我回了邮件,原文:

“图中示意确实有误,其实那个clk高电平输出应该作为前两级寄存器的使能信号,而非相与。我会尽快勘误,谢谢”

感谢作者

我的理解是:接DATA信号的两级寄存器用二分频时钟做使能信号,增加了恢复时间,从而减小了亚稳态的概率。