例化altera的altgx Ip核

时间:10-02

整理:3721RD

点击:

我用altera的 FPGA ,使用 QUARTUS 9.1 的 megawizard plug-in manager 例化ALTGX 模块 。

但为什么不管我怎么输入,tx_datain=随机数 或 x(不定数),其结果tx_dataout的输出都是K28.5的串行数据 ,始终不变。请教!

以下代码是我的testbench;

但为什么不管我怎么输入,tx_datain=随机数 或 x(不定数),其结果tx_dataout的输出都是K28.5的串行数据 ,始终不变。请教!

以下代码是我的testbench;

- `timescale 100ps/100ps

- module serdes_top_tb (/*AUTOARG*/) ;

- reg cal_blk_clk, pll_inclk;

- reg [15:0] tx_datain;

- reg tx_digitalreset;

- reg clk_2500;

- reg [1:0] tx_ctrlenable;

- wire tx_clkout, tx_dataout;

- wire [4:0] tx_datain_5L,tx_datain_5H;

- wire [2:0] tx_datain_3L,tx_datain_3H;

- assign tx_datain_5L=tx_datain[4:0];

- assign tx_datain_3L=tx_datain[7:5];

- assign tx_datain_5H=tx_datain[12:8];

- assign tx_datain_3H=tx_datain[15:13];

- initial

- begin

- tx_ctrlenable=2'b00;

- end

- initial

- begin

- tx_digitalreset=0;

- #3000 tx_digitalreset=1;

- end

- initial

- begin

- clk_2500=0;

- forever #200 clk_2500=~clk_2500;

- end

- initial

- begin

- pll_inclk=0;

- forever #2000 pll_inclk=~pll_inclk;

- end

- initial

- begin

- cal_blk_clk=0;

- forever #2000 cal_blk_clk=~cal_blk_clk;

- end

- always@(posedge pll_inclk or negedge tx_digitalreset)

- if(!tx_digitalreset)

- tx_datain<=16'b101_1110_101_1110;

- else

- begin

- tx_datain[15:8]<={$random}%256;

- tx_datain[7:0]<={$random}%256;

- end

- serdes U1 (/*AUTOINST*/

- // Outputs

- .tx_clkout (tx_clkout),

- .tx_dataout (tx_dataout),

- // Inputs

- .cal_blk_clk (cal_blk_clk),

- .pll_inclk (pll_inclk),

- .tx_ctrlenable (tx_ctrlenable),

- .tx_datain (tx_datain),

- .tx_digitalreset (tx_digitalreset));

- endmodule // serdes_top

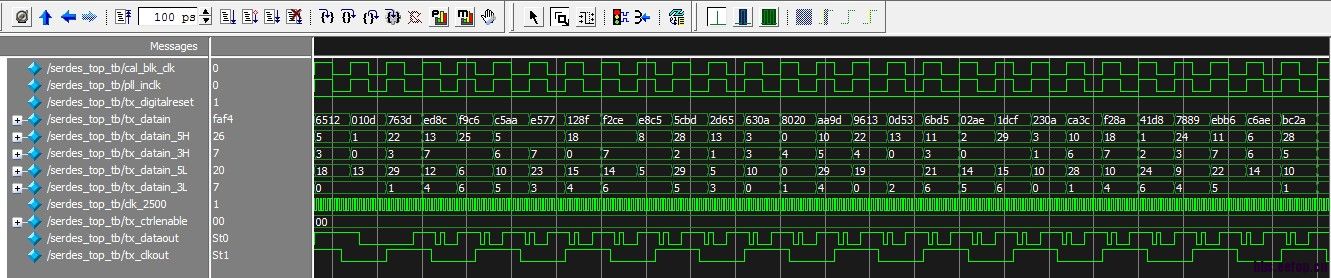

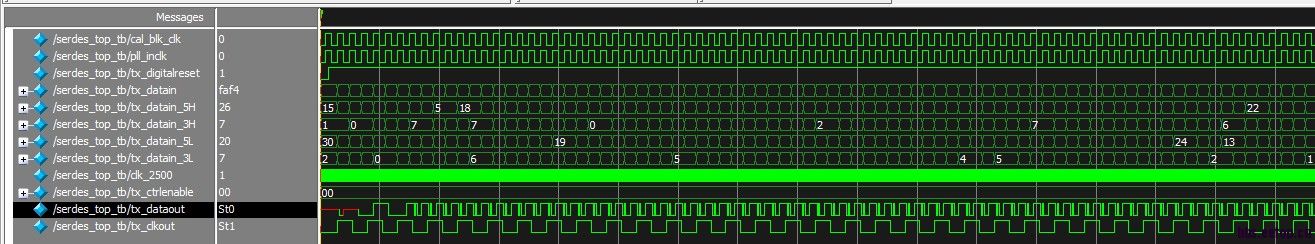

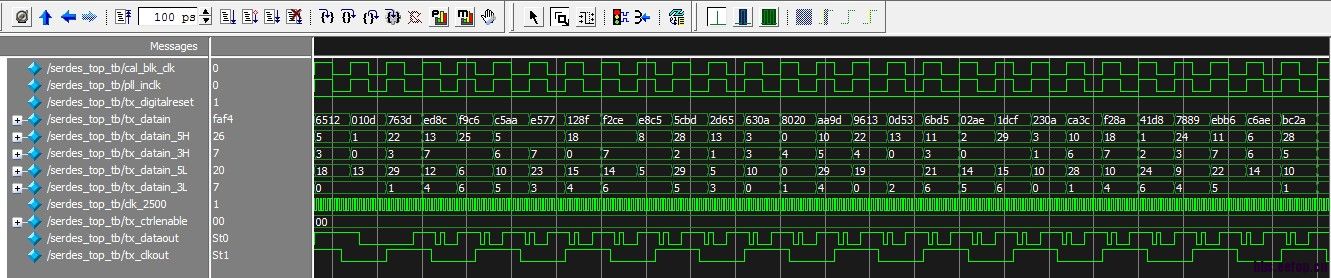

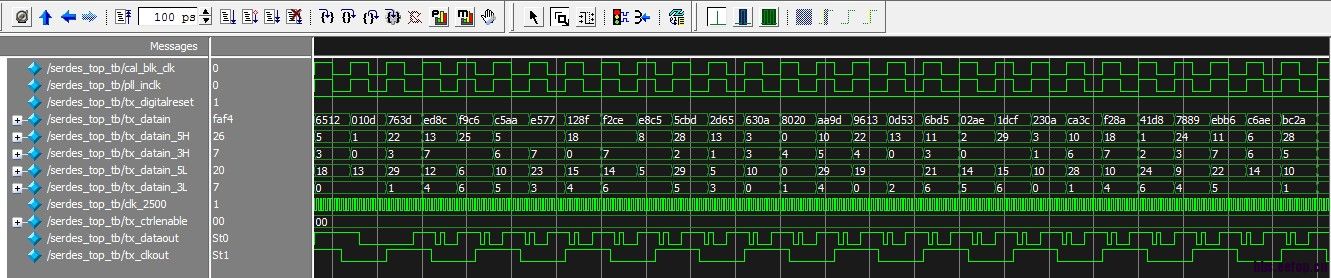

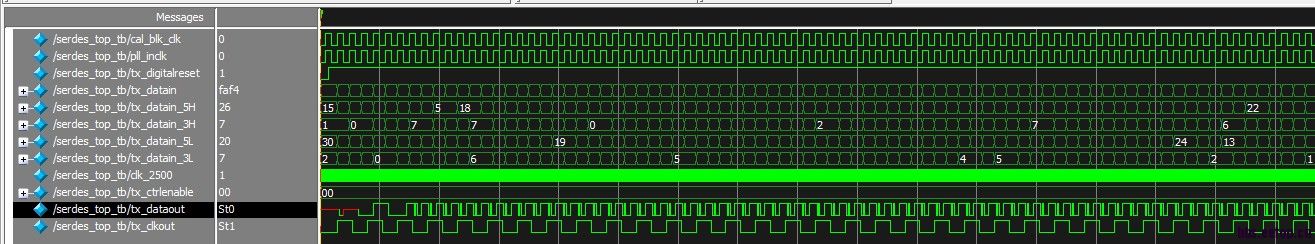

这是我用modelsim的仿真波形

这是我用moselsim仿真的波形 tx_dataout是串行输出波形 一直是k28.5的串行波形

1.首先确认你的testbench里面的时钟和你例化IPCORE的pll_inclk是否一样?

2.在发送数据的时候,需要定期的发送K28.5,也就是把tx_ctrlenable置为高电平,同时把数据置为BC?

3.ALTERA GXB模块对复位时序是有要求的,确认你的复位时序是否满足。