一个简单的关于时序的问题

最近学verilog,还没有涉及时序仿真,关于时序有一个问题很困惑,求各路大神分析:

代码:

always @(posedge clock)

if(valid) cnt = cnt+1;

else if(!valid) cnt = 0;

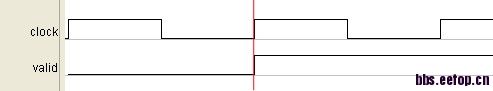

假设输入信号在理想情况下,clock和valid的上跳沿是重合的,在clock的上跳沿看不能分辨valid是0还是1,如下图;

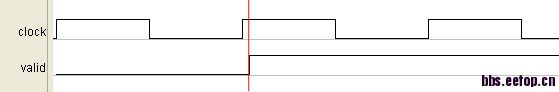

为了避免出现这样的情况,我试图通过时序约束将valid的上跳沿控制在clock的上跳沿偏后一点的地方,如下图;

不知道这样时序约束是否可行

valid信号本身需要是clock时钟域下的信号,这样就可以按同步设计考虑。

valid是clock时钟域下的信号没错,但是如果在理想情况下:clock的上跳沿会和valid(输入信号,不受我控制)的上跳沿重合

if语句综合出来是组合电路, 应该以当前值为条件吧,仿真的时候认为 valid是1

我觉得应该先有数据vaild,再出现时钟上升沿,因为要满足建立时间和保持时间的约束条件要求!

功能仿真的话加不加延时无所谓的。

仿真归仿真,但是我想知道实际的时候(也就是经过时序约束之后)的情况应该是怎么样的

如果是异步signal,则需要先进行同步处理,存在一拍的沿打沿是正常的,同步逻辑,则不存在问题。

的确是同步逻辑,但是出现的沿打沿怎么解释呢?

持相同意见 不过你只要避免vaild的跳变沿和时钟上升沿重合就可以了

实际电路中,CLK时钟域的产生的信号都会在时钟沿之后跳变的,大概tCK-Q,昨天不是讨论过么。

另外,时序逻辑的赋值最好用<=, 组合逻辑才用=。

仿真上看,是一样的

加了延时,仅仅是为了便于看波形而已,不加也是没有关系的

实际上,如果valid信号是外部输入信号的话需要做同步处理,之后才能按照同步时钟域处理,也就不存在你说的沿打沿的情况了

同步逻辑的话,在FPGA内部是可以保证不会出现沿打沿的,前提是只要时序满足约束就可以了。如果是外部管脚送进来的信号(系统同一个时钟)

,那么就要正确约束输入的最大最小延时(即约束Tsu和Th)

实际情况的话,如果两个沿重叠这个地方会出现竞争的现象,必须用非阻塞赋值

学习中。

上升沿重叠的这种情况,我觉得是取0,因为是取前一个时刻的值,你仿真试试看吧,本人愚见

上升沿是VALID应该为0,因为VALID从0变到0有个时间的。

你这个是功能仿真还是时序仿真

如果是功能仿真的话,这个应该是正常的吧?

时序仿真的话,信号肯定有延迟了。

仿真的时候不用考虑的

至于你说的实际情况:首先为满足setup hold时间 综合还有布局等工具会自己做一个时钟树,在原有的信号线上加上buffer 反向器等等 之后还考虑线延迟 和 器件延迟

最后生成的波形 应该是 valid数据先到 clk后到 具体时间差不多 跟你插入时钟树时用的延迟文件有关

前仿的数据都是没有延迟的。

实际中是要避免这种情况的,会出现亚稳态的情况,仿真就无所谓了。

对于赋值语句,同步逻辑中最好用<=,不过像你这样一个分支只有一条语句的话用哪个都是可以的。