自己一直无法理解赋值延时,请教一下各位。

时间:10-02

整理:3721RD

点击:

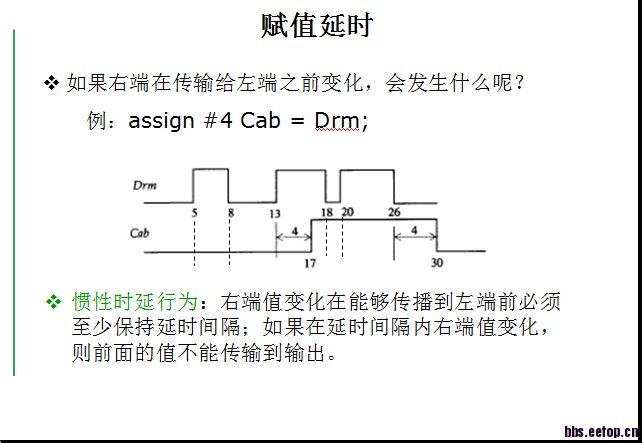

自己老是理解不了赋值延时,比如下面这张图

我老是觉得,输出波形是输入波形的复制,就是加了个延时,

为什么在延时间隔内右端信号值变化,左边就不能显示了呢?

你这是在哪里看到的破书,这不是误人子弟吗

追求这种东东有任何意义吗?

或许建模时候有用吧。

实际设计很少用到。 那个延时放到=号右边就和你理解的一样了

其实这个很好理解嘛,就是只能记录变化的时候的后四秒的值,如果这这期间又发生改变了,则重新计时 仅此而已

我觉得应该从晶体管级别来理解这个问题!输出是高电平还是低电平是由输出点上的那个电容的电荷量来决定的,也就是电容通过充放电来实现1和0之间的转换。在数字电路中,1和0都有一定的电压噪声容限。

就拿最简单的反相器来说,它由一个PMOS和一个NMOS组成,假设原来的稳定状态为输入为0(输出为1),如果现在将输入由0变为1的话,输出如果要由1变为0是需要通过输出点的电容放电才能实现的,也就是门都有一段时间的延迟,如果输入只在1上稳定很短时间就又变回了0的话,也就是输出接点的电容还没有来得及放电到可以用0来表示的时候由开始充电了,所以其实从输出上来看,一直都是1.

(当然在Verilog仿真的时候如果没有设定延迟,门原语的延迟默认都为0,所以可以瞬间变化)。

assign #4 cab=drm; //drm变化4ns后,采样drm即时值。

assign cab= #4 drm; //输出波形是输入波形的复制,就是加了个4ns延时

实际上用得很少,不用深究

如此所说,建模的时候或许有用。

顶7楼,

其实这个也只是为了说明在仿真建模时具体语法的意义,理解其具体意思就可以了

不能说完全没有意义,要不然verilog就不会弄出这些用法了