使用Verilog实现I2C时在仿真上遇到的困难,请各位赐教

时间:10-02

整理:3721RD

点击:

这是我的毕业设计题目《基于fpga的I2C接口设计》,我现在正在用Verilog尝试实现输出正确的波形,程序的流程基本是这样:键盘输入使I2C从设备产生中断信号,cyclone接到中断并响应,拉低sda开始发送数据,依次发送7位从机地址+写控制位,8位命令字,7位从机地址+读控制位(中间需要从机响应),然后开始接收来自从机的数据。

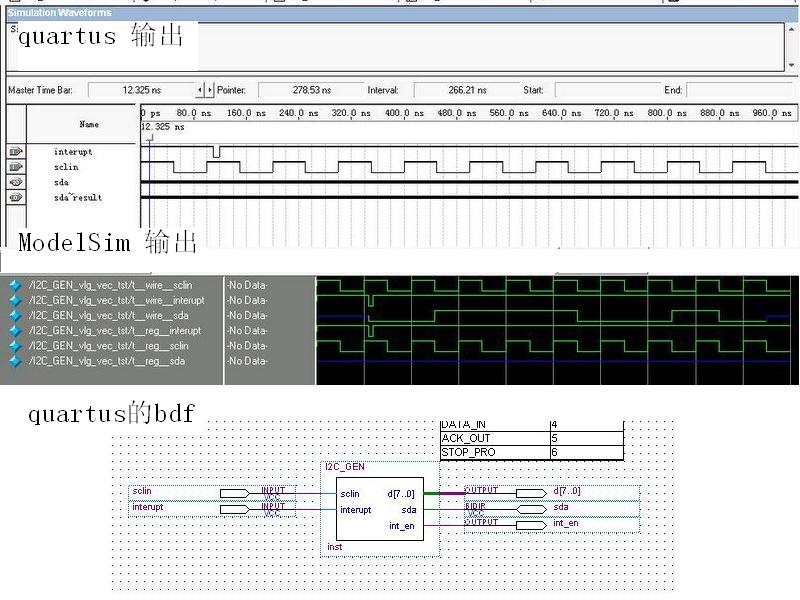

但是我在使用quartus和modelsim仿真时遇到了下面的问题:在quartus中编辑.vwf文件进行仿真没有输出,将.vwf文件转成.v文件在modelSim中仿真输出了正确的波形。

请问大家上面的情况可能是哪里出现问题了呢?是我程序的问题,测试数据的问题还是软件设置的问题,请大家赐教。下面是波形图。

但是我在使用quartus和modelsim仿真时遇到了下面的问题:在quartus中编辑.vwf文件进行仿真没有输出,将.vwf文件转成.v文件在modelSim中仿真输出了正确的波形。

请问大家上面的情况可能是哪里出现问题了呢?是我程序的问题,测试数据的问题还是软件设置的问题,请大家赐教。下面是波形图。

波形图

题目跟我的差不多,不过我用的是VHDL,目前能力有限,飘过~

sda是双向的,你的i2c slave做的对不对哦,主意一下ack信号!

进行写操作的时候,i2c slave必须给出相应的ack,slave中的状态才能继续下去

读的时候也一样,请主意这些

sda是双向的,你的i2c slave做的对不对哦,主意一下ack信号!

进行写操作的时候,i2c slave必须给出相应的ack,slave中的状态才能继续下去

读的时候也一样,请主意这些

以前有人问过这样的问题,modelsim仿真不需要综合,是功能仿真,所以能够出现正确波形

竟然看到自己三年前的帖子,哈哈。这个问题还真是弱啊,当时写的代码都是不可综合的,自然在quartus里没有结果。

7楼说的提醒在写代码的时候一定要知道写的代码是否是可以综合的,建议要好好看看可以综合代码的风格。

还有就是做软件写的是程序,我们写的叫代码,不要将定义给搞混了。