各位大侠,帮忙看一段代码,谢谢

时间:10-02

整理:3721RD

点击:

各位大侠,我想实现一个移位寄存器,输入输出关系如下:

input: data_in: 1 2 3 4 5 6 7 8 9

output: line2 : x 1 2 3 4 5 6 7 8 9

output: line1 : x x x x 1 2 3 4 5 6 7 8 9

output: line0 : x x x x x x x 1 2 3 4 5 6 7 8 9

代码是有问题的帮忙看一下,谢谢了

module linebuffer(reset,clk,data_in,line2,line1,line0,count);

input[7:0] data_in;

input clk;

input reset;

output[7:0] line1,line0;

output[3:0] count;

reg[7:0] data[9:0];//用到10个寄存器方便存储之前的数据

reg[3:0] count;

reg[7:0] line2,line1,line0;

always@(posedge clk or posedge reset)

begin

if(reset)

begin

data[count]<=0;

count=0;

end

else

begin

count<=count+1;

line2<=data_in;

end

end

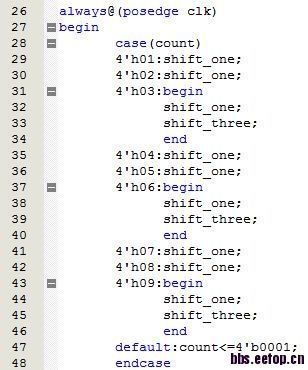

always@(posedge clk)

begin

case(count)

4'h01:shift_one;

4'h02:shift_one;

4'h03:begin

shift_one;

shift_three;

end

4'h04:shift_one;

4'h05:shift_one;

4'h06:begin

shift_one;

shift_three;

end

4'h07:shift_one;

4'h08:shift_one;

4'h09:begin

shift_one;

shift_three;

end

default:count<=4'b0001;

endcase

end

task shift_three;

begin

line1<=data[count-2];line1<=data[count-1];line1<=data[count];

line0<=data[count-2];line0<=data[count-1];line0<=data[count];

end

endtask

task shift_one;

data[count]<=data_in;

endtask

endmodule

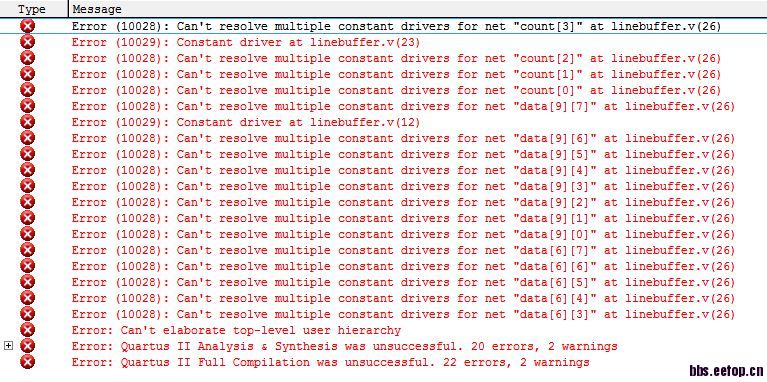

仿真时这一部分有错误,是关于count和寄存器data的赋值

,没人帮忙呀

can't resolve multiple constant drivers for net

两个进程里都有同一个条件判断的话,会产生并行信号冲突的问题。

同一个信号不允许在多个进程中赋值,否则则为多驱动。

进程的并行性决定了多进程不同能对同一个对象进行赋值。

怎么解决?

跟我刚学一样的错误

解决方案,只能在一个always块里面对一个寄存器ff1赋值,不能在其他always块中又对ff1赋值

default:count<=4'b0001;

把这个删了

看起来很简单的事情,,不知道你的代码在搞什么。你要干嘛问题也没描述清楚

寄存器延迟就足够了

用得着这么写?

不是自己给自己找麻烦

已解决问题,谢谢上面的各位

上面的代码有错的部分是

line1<=data[count-2];line1<=data[count-1];line1<=data[count];

line0<=data[count-2];line0<=data[count-1];line0<=data[count];

不可对同一变量赋多次值(在同一上升沿)

关于移3个输入,上面的

"MOSFET"

说的很正确,谢谢了

用寄存器的延时即可实现

定义两个寄存器

代码部分如下:

reg[7:0] data1[2:0];

reg[7:0] data0[2:0];

...

line2<=data_in;

data1[count1]<=line2;

data0[count0]<=line1;

...

count1<=count1+1;

...

count0<=count0+1;

...

谢谢