为什么我的敏感列表不全,但是仿真的时候确实正确的呢?

时间:10-02

整理:3721RD

点击:

module com_logic(a,b,c,out1,out2,out3);

input a,b,c;

output out1,out2,out3;

reg out1,out2;

always @(a)

out1 = a & b & c;

always @(*)

out2 = a & b & c;

assign out3 = a & b & c;

endmodule

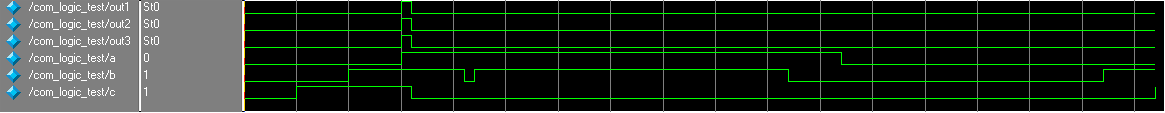

输出out1 out2 out3的波形完全一样?

out1的敏感列表只有a,b和c变化时out2应该不会变化啊?

a变1后维持不变,变化b和c,当c变0后,out1 2 3也都变0了?

input a,b,c;

output out1,out2,out3;

reg out1,out2;

always @(a)

out1 = a & b & c;

always @(*)

out2 = a & b & c;

assign out3 = a & b & c;

endmodule

输出out1 out2 out3的波形完全一样?

out1的敏感列表只有a,b和c变化时out2应该不会变化啊?

还是全了好呗

小编肯定是测试向量不够啊!

out2和out3肯定是一样的,而out1就不一定了

如果电路功能是无条件循环执行的,可以没有敏感信号列表。我也认为OUT2和OUT3的结果应该相同,

我用你的代码仿出来的结果out1和out2,out3的结果是不同的,

我给的a,b,c的信号是:a不变,任意改变b和c的值,结果就出来了,out1的值是不随着b和c的变化而变化的。然后改变a的值,发现out1的值是随着a的值改变的

你给的信号源肯定不够,测试不够完全

测的情况不全,out1的值是不随着b和c的变化而变化的。

敏感变量不影响实际生成电路的功能 只是语法建议加上敏感变量 自己调试方便 也有一些专门的生成电路线路保护的措施 一般来说 简单的逻辑不加只是多一些警告而已

自己写一个测试文件吧!

EricLab 你用的什么仿真,我用modelsim6.2

a变1后维持不变,变化b和c,当c变0后,out1 2 3也都变0了?