再问一个关于时序的问题~

时间:10-02

整理:3721RD

点击:

一直有个不明白的地方,求指教~

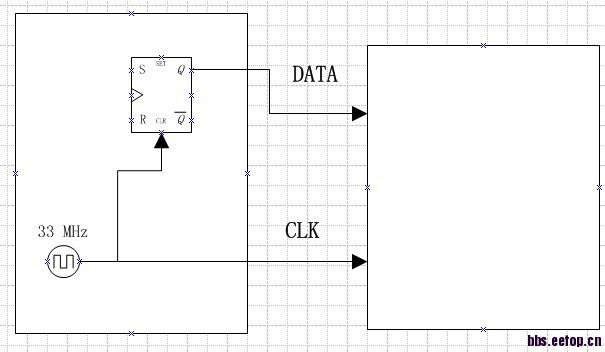

我随便画了个图,比如上图系统,采用源同步设计,第二个模块接收来自第一个模块的数据和时钟,数据和时钟如图,第二个模块肯定会有自己的建立保持时间要求。

但是一般第一个模块设计的时候,基本我们都会这样写吧:

always @(posedge clk)

begin

data <= din;

end

按照代码和综合的RTL电路,很容易理解即CLK上升沿和DATA是同时输出到PAD的,甚至DATA的延迟还要大吧?

这样做似乎也不影响设计,很多时候都能跑通。

但是我不理解的是,这样显然是不满足下一个模块的建立保持要求的呀。?

前辈能不能解释下这个疑问,看我哪地方错了?

多谢!

因为他都是放在一起编译的,并非做成一块一块相连的电路

模块间如果分别综合的话,需要设定input delay, 工具根据你设定的delay值和输入的逻辑会分别在clock和data上加入合适的buffer,以便使输入模块的第一级寄存器可以可靠的捕获数据。

你要把你这个图扩展一下,你只画了你本地的设计,那么对端的设计呢?画全了就像下面的图了。

你在某个CLK周期把数据flop out出去,那么对端器件在CLK的下一个周期采样。你理解了吗?

哦 明白了 多谢!