FPGA中使用modelsim的问题

时间:10-02

整理:3721RD

点击:

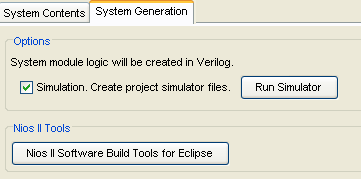

我用的是quartusII 10.0搭的一个sopc系统,然后照着书本上做了一个例子,就是简单的测试灯的程序(用的是nios II IDE),然后后来我又想是否可以在下板子之前先用modelsim做前仿,于是系统搭好之后在generate之前我勾选了如下图

做完软件编译等步骤之后我就从文件目录中找到了****_sim的文件夹,从里面找到了setup_sim的文件(do文件),打开后选取了vlog +incdir+.. ../adc_avalon.v;这样的一句话,copy到modelsim中编译,结果出现以下错误

# ** Error: ../cpu_0.v(1): syntax error, unexpected non-printable character 0x8b

# ** Error: ../cpu_0.v(1): syntax error, unexpected $undefined, expecting "class"

# E:/software/modelsim/win32/vlog failed.

忘高手解答,谢谢。

做完软件编译等步骤之后我就从文件目录中找到了****_sim的文件夹,从里面找到了setup_sim的文件(do文件),打开后选取了vlog +incdir+.. ../adc_avalon.v;这样的一句话,copy到modelsim中编译,结果出现以下错误

# ** Error: ../cpu_0.v(1): syntax error, unexpected non-printable character 0x8b

# ** Error: ../cpu_0.v(1): syntax error, unexpected $undefined, expecting "class"

# E:/software/modelsim/win32/vlog failed.

忘高手解答,谢谢。

为什么不直接在modelsim中执行这个.do脚本文件?