一个基础电路问题

时间:10-02

整理:3721RD

点击:

[attach]363922[/attach]

[attach]363923[/attach]

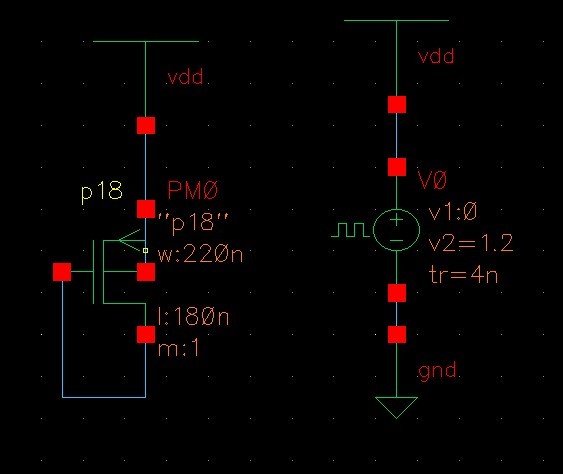

对PMOS电路,将S和B接在一起,外加一个线性递增的电压到1.2V。G和D端接在一起,悬空。电路图如图1所示,

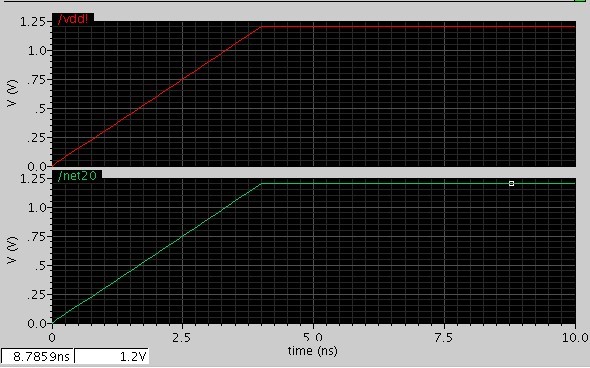

测得结果如图2所示。

可以看出D和S端是一致的,这与理论不一致。请问是什么原因?麻烦大牛指教下。

谢谢。

[attach]363923[/attach]

对PMOS电路,将S和B接在一起,外加一个线性递增的电压到1.2V。G和D端接在一起,悬空。电路图如图1所示,

测得结果如图2所示。

可以看出D和S端是一致的,这与理论不一致。请问是什么原因?麻烦大牛指教下。

谢谢。

[attach]363926[/attach]

图1

不好意思,不会发图,发了几次。

图上net20是哪点啊?

就是g、d相连接的那点

我倒是觉得合理,你一端放开了,仿真器只能连一个超大的接地电阻进来来构成仿真回路(用来取代无穷大的开路电阻,具体值可以查manual),MOS管的开态还是关态的电阻都远小于你这个开路的无穷大电阻,当然要跟随你电源的变化。

那前提不是管子必须导通嘛?用上图的激励可以说管子内部电容是导通了,但是换成直流电压,管子内部电容就无法导通,怎么还会跟随呢?我试了试直流电。

就是给个很小的直流的电压,管子没导通,但是漏端的电压也是跟随的这又怎么解释呢

支持andyfan 的观点。

主要是DS之间的阻抗比仿真中加的D到地的阻抗要小很多,所以D跟随S

管子的导通和关闭是相对的,除非你用理想模型。我的意思是即便管子在非开通状态,也还是有漏电的吧,哪这个时候的关态电阻也远小于哪个无穷大的开路电阻,因为开路不会有漏电,哪当然还是跟随。

如果你用的是理想模型,哪我真不知道是什么原因了

过来看看!