调用ROM出错

显示的warning是:Xst:2036 - Inserting OBUF on port <sinwave<0>> driven by black box <core>. Possible simulation mismatch.其中sinewave是我定义的sine波数据输出口,core是我的rom核。

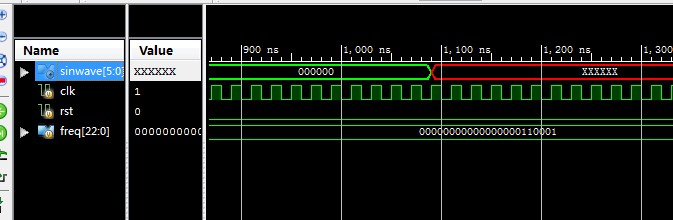

读出的数据总是显示XXXXX,到底是怎么回事?

仔细看下ROM的的时序,地址,时钟都按要求给了吗

你生成的ROM没有添加到工程里面,找不到文件,所以 black box 了。

ROM的数据你按要求制作的吗?另外,HEX文件的路径,在CORE生成文件中是什么样路径?最好是当前路径,然后仿真的时候你把HEX放在仿真work目录下

感谢楼上3位,你们说的问题我检查了,应该不是出在这些方面的

继续等高手的建议!可能是自己哪地方疏忽了,贴出程序来请过路高手帮忙看下,程序很短。

module genwave(

input clk,

input rst,

input [22:0]freq,//固定的分频值

output [5:0] sinwave

);

reg rom_read;

reg [5:0]cnt,cnt1;

always@(posedge clk)begin//计数器

if(rst)

rom_read<=0;

else

if(cnt1==freq-1)//

rom_read<=1;

else

rom_read<=0;

end

always@(posedge clk)begin //对系统时钟分频产生读ROM时钟

if(rst)

cnt1<=0;

else if(cnt1==freq-1)//

cnt1<=0;

else

cnt1<=cnt1+1;

end

always@(posedge rom_read)begin//每读一次ROM就计数一次,ROM中共50个数据,只需50个时钟就可以读完一次,以计数器的值作为ROM的地址

if(rst)begin

cnt<=0;

end

else

if(cnt==49)

cnt<=0;

else

cnt<=cnt+6'd1;

end

core sine(

.clka(rom_read),

.addra(cnt),

.douta(sinwave)

);

endmodule

去掉最后一个always并改成下面试试,:

always@(posedge clk)begin//计数器

if(rst)

rom_read<=0;

cnt<=0;

else

if(cnt1==freq-1)//

rom_read<=1;

cnt<=cnt+1;

else

rom_read<=0;

end

PS:建议用低电平复位

感谢7楼,我昨天改成这个了,还是不行,问题应该不是出在这里

小编用的不是altera,呵呵,我也不太明白,不过帮你查了一个,警告类似,最后仿真的结果输出是高阻,结论可能是版本不对,仅作为提示。

给不了链接,你自己去google上查吧

多谢各位,问题昨天解决了,确实是在计数上出了问题,我换了一种方式编程就好了,至于上面的分频和计数有什么问题我还没想出来。

不知你换成什么“编程方式”把问题解决了,能说详细点吗?或者把你“正确”的方式也贴出来让大家帮你找找原因

我也比较好奇这个问题。从warning来看应该是仿真软件找不到core这个模块,一般这样都是只拷贝了.v而没有拷贝初始化文件

集成的仿真器确实不太好用,很多都不认识