求在FPGA中运用浮点核的成功范例

求大虾们指教啊!

在FPGA中还是用定点算法吧,浮点算法是劳民伤财啊。

浮点也不是很难,和32位定点也差不多,绝对可以使用。

嗯,浮点是挺费资源的。不过,只要能实现功能,用什么倒是无所谓了。

component float_divide

port (

a: IN std_logic_VECTOR(31 downto 0);

b: IN std_logic_VECTOR(31 downto 0);

operation_nd: IN std_logic;

operation_rfd: OUT std_logic;

clk: IN std_logic;

sclr: IN std_logic;

ce: IN std_logic;

result: OUT std_logic_VECTOR(31 downto 0);

rdy: OUT std_logic);

end component;

tofudian1 : float_divide

port map (

a => shuju1_d,

b => shuju2_d,

operation_nd => op_nd_d,

operation_rfd => op_rfd_d,

clk => clk,

sclr => sclr_d,

ce => ce_d,

result => feng_fudian_60,

rdy => ready_d);

process(ok_fd)

begin

if ok_fd='1' then

ce_d<='1';

else

ce_d<='0';

end if;

end process;

process(clk,ce_d)

begin

if ce_d='1' then

if clk'event and clk='1' then

if count_d="10" then

count_d<="10";

else

count_d<=count_d+'1';

end if;

end if;

end if;

end process;

process(count_d)

begin

if count_d="01" then

sclr_d<='1';

else

sclr_d<='0';

end if;

end process;

process(op_rfd_d)

begin

if op_rfd_d'event and op_rfd_d='1' then

shuju1_d<=xiaoshu_fudian;

shuju2_d<=liushi;

op_nd_d<='1';

end if;

end process;

process(ready_d)

begin

if ready_d='1' then

ce_a<='1';

else

ce_a<='0';

end if;

end process;

process(ce_a,clk)

begin

if ce_a='1' then

if clk'event and clk='1' then

if count_a="10" then

count_a<="10";

else

count_a<=count_a+'1';

end if;

end if;

end if;

end process;

process(count_a)

begin

if count_a="01" then

sclr_a<='1';

else

sclr_a<='0';

end if;

end process;

process(op_rfd_a)

begin

if op_rfd_a'event and op_rfd_a='1' then

shuju1_a<=feng_fudian_60;

shuju2_a<=du_fudian;

op_nd_a<='1';

end if;

end process;

这是用浮点核做除法中的几段代码,还请指点一二。

bang ding

?绑定?

对浮点核的运用已经试验成功了,下一步准备对浮点核的重复利用,以节省有限的资源。谢谢大家的关注!

我用过,我是把小数移位做整数处理,然后再移回来

这种代码实在是无法接受o(╯□╰)o

还请指点啊,jackertja.

嗯,这倒是个不错的方法!

process(ok_fd)

begin

if ok_fd='1' then

ce_d<='1';

else

ce_d<='0';

end if;

end process;

这种代码没什么意义,ce_d就是ok_fd,如果是为了debug时候便于理解,直接ce_d<= ok_fd;就可以了。

----------------------------------------------------------------------

process(clk,ce_d)

begin

if ce_d='1' then

if clk'event and clk='1' then

if count_d="10" then

count_d<="10";

else

count_d<=count_d+'1';

end if;

end if;

end if;

end process;

这是希望综合成门控时钟还是什么别的电路呢?count_d是不是只计数一次,之后就永远停在"10"了呢?

----------------------------------------------------------------------

process(op_rfd_a)

begin

if op_rfd_a'event and op_rfd_a='1' then

shuju1_a<=feng_fudian_60;

shuju2_a<=du_fudian;

op_nd_a<='1';

end if;

end process;

这是希望把op_rfd_a作为时钟吗?有什么特别的需求?

op_nd_a永远为'1'有没有问题?

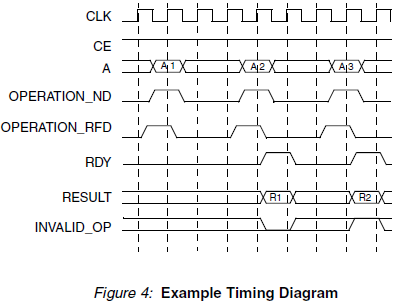

嗯,你说得很对呢。我这个IP核只用了一次,如果我想重复利用IP核,这个代码应该怎样写呢?那个operation_rfd怎么用,还是没真正搞懂。我看帮助文档里有这样一个图,它的代码应该是怎样的呢,请指点,谢谢了!