FPGA的RTL综合经验 讨论

时间:10-02

整理:3721RD

点击:

先上一段代码:module(signal,clk,reset,out)

input signal;

input clk;

input reset;

output out;

reg [3:0] shift_reg;

always@(posedge clk or negedge reset)

if(!reset)

shift_reg <= 4'b0;

else

begin

shift_reg[0] <= signal;

shift_reg[1] <= shift_reg[0];

shift_reg[2] <= shift_reg[1];

shift_reg[3] <= shift_reg[2];

end

assign out= (shift_reg) ? 1'b1 : 1'b0;

endmodule

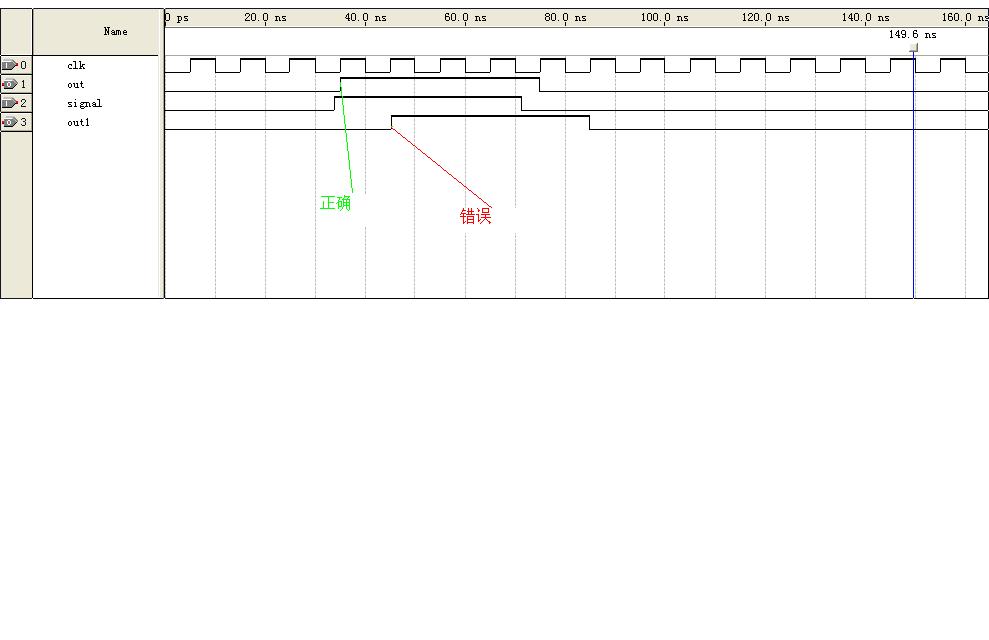

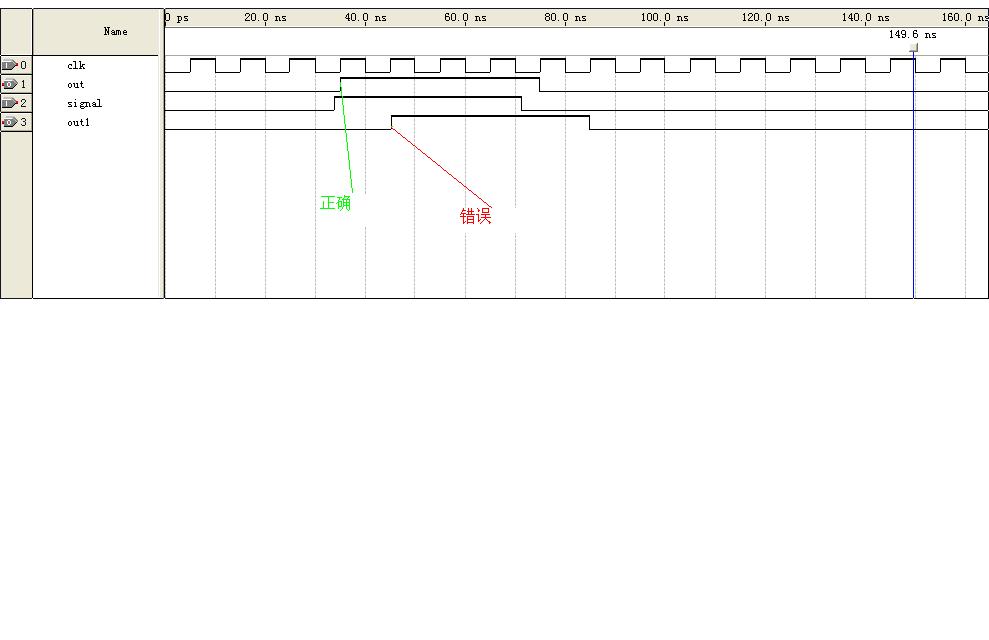

综合后signal 会连接到shift_reg[0]的sload端而不是shift_reg[0]的D端口,所以在时钟沿到来时,signal信号已经打到shift_reg[0]中,而不是下一个时钟周期才打到寄存器中。如下图所示:

input signal;

input clk;

input reset;

output out;

reg [3:0] shift_reg;

always@(posedge clk or negedge reset)

if(!reset)

shift_reg <= 4'b0;

else

begin

shift_reg[0] <= signal;

shift_reg[1] <= shift_reg[0];

shift_reg[2] <= shift_reg[1];

shift_reg[3] <= shift_reg[2];

end

assign out= (shift_reg) ? 1'b1 : 1'b0;

endmodule

综合后signal 会连接到shift_reg[0]的sload端而不是shift_reg[0]的D端口,所以在时钟沿到来时,signal信号已经打到shift_reg[0]中,而不是下一个时钟周期才打到寄存器中。如下图所示:

没觉得有错误,波形图out1是什么信号?

这句是什么用意哦

assign out= (shift_reg) ? 1'b1 : 1'b0;

sload和D不是相当的吗?

从代码上看不出时钟沿到时,信号已经打入reg

assign out= (shift_reg) ? 1'b1 : 1'b0;

如果这句话的意思是指补码格式的shift_reg大于零就输出1,那么程序是没问题的。

PS:DFF有D端,CLK端,Q端,RST端,ENA端。你这里的sload端是从哪里来的,RTL视图里怎么会钻出sload端来?

signal连接到sload没有错,我没猜错的话sload应该是synchronize load。它可以让flop的q端置为1.这和你写的Verilog并没有冲突。不过仔细看看,signal应该还要连接reset吧,要不然当signal为0时怎么reset shift_reg[0]=0呢?