请问FPGA中复位的问题

时间:10-02

整理:3721RD

点击:

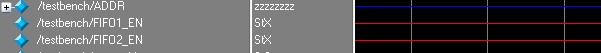

各位好,上回问到我想用DSP读取我FPGA中八个FIFO中的数据,现在我需要在FPGA中产生八个FIFO的读使能信号,用的是地址译码,我把地址ADDR放在了敏感列表中,但是出现了两个问题1:当我的地址不是八个FIFO中任何一个的地址或者是高阻时,我用default语句将八个使能信号全设为低电平,但是仿真出来后却是不定值:

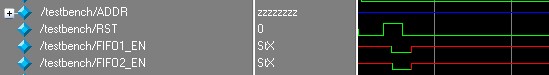

2:我想设一个复位信号,复位后所有的读使能都为低电平,但是由于我已经把ADDR放在了敏感列表中,如果把posedge RST也放进去会报错,因为不能同时检测跳变沿和电平,于是我把RST信号也改成了电平检测,即always@(ADDR or IS or RST),但是使能信号好像没有被复位:

是什么原因呢?是不是复位信号只能用跳变沿检测才会有效?那怎样才能把地址总线的变化和复位信号的变化放在一个always里呢?谢谢!

下面是我的源程序,小弟不才,程序可能不规范请拍砖!parameter FIFO1=8'h00,

FIFO2=8'h01,

FIFO3=8'h02,

FIFO4=8'h03,

FIFO5=8'h04,

FIFO6=8'h05,

FIFO7=8'h06,

FIFO8=8'h07;

always@(ADDR or IS or RST)

begin

if(RST)

begin

FIFO1_EN=1'b0;

FIFO2_EN=1'b0;

FIFO3_EN=1'b0;

FIFO4_EN=1'b0;

FIFO5_EN=1'b0;

FIFO6_EN=1'b0;

FIFO7_EN=1'b0;

FIFO8_EN=1'b0;

end

else

if(~IS)

case(ADDR)

FIFO1:begin

FIFO1_EN=1'b1;

FIFO2_EN=1'b0;

FIFO3_EN=1'b0;

FIFO4_EN=1'b0;

FIFO5_EN=1'b0;

FIFO6_EN=1'b0;

FIFO7_EN=1'b0;

FIFO8_EN=1'b0;

end

FIFO2:begin

FIFO1_EN=1'b0;

FIFO2_EN=1'b1;

FIFO3_EN=1'b0;

FIFO4_EN=1'b0;

FIFO5_EN=1'b0;

FIFO6_EN=1'b0;

FIFO7_EN=1'b0;

FIFO8_EN=1'b0;

end

FIFO3:begin

FIFO1_EN=1'b0;

FIFO2_EN=1'b0;

FIFO3_EN=1'b1;

FIFO4_EN=1'b0;

FIFO5_EN=1'b0;

FIFO6_EN=1'b0;

FIFO7_EN=1'b0;

FIFO8_EN=1'b0;

end

FIFO4:begin

FIFO1_EN=1'b0;

FIFO2_EN=1'b0;

FIFO3_EN=1'b0;

FIFO4_EN=1'b1;

FIFO5_EN=1'b0;

FIFO6_EN=1'b0;

FIFO7_EN=1'b0;

FIFO8_EN=1'b0;

end

FIFO5:begin

FIFO1_EN=1'b0;

FIFO2_EN=1'b0;

FIFO3_EN=1'b0;

FIFO4_EN=1'b0;

FIFO5_EN=1'b1;

FIFO6_EN=1'b0;

FIFO7_EN=1'b0;

FIFO8_EN=1'b0;

end

FIFO6:begin

FIFO1_EN=1'b0;

FIFO2_EN=1'b0;

FIFO3_EN=1'b0;

FIFO4_EN=1'b0;

FIFO5_EN=1'b0;

FIFO6_EN=1'b1;

FIFO7_EN=1'b0;

FIFO8_EN=1'b0;

end

FIFO7:begin

FIFO1_EN=1'b0;

FIFO2_EN=1'b0;

FIFO3_EN=1'b0;

FIFO4_EN=1'b0;

FIFO5_EN=1'b0;

FIFO6_EN=1'b0;

FIFO7_EN=1'b1;

FIFO8_EN=1'b0;

end

FIFO8:begin

FIFO1_EN=1'b0;

FIFO2_EN=1'b0;

FIFO3_EN=1'b0;

FIFO4_EN=1'b0;

FIFO5_EN=1'b0;

FIFO6_EN=1'b0;

FIFO7_EN=1'b0;

FIFO8_EN=1'b1;

end

default:begin

FIFO1_EN=1'b0;

FIFO2_EN=1'b0;

FIFO3_EN=1'b0;

FIFO4_EN=1'b0;

FIFO5_EN=1'b0;

FIFO6_EN=1'b0;

FIFO7_EN=1'b0;

FIFO8_EN=1'b0;

end

endcase

else

begin

FIFO1_EN=1'b0;

FIFO2_EN=1'b0;

FIFO3_EN=1'b0;

FIFO4_EN=1'b0;

FIFO5_EN=1'b0;

FIFO6_EN=1'b0;

FIFO7_EN=1'b0;

FIFO8_EN=1'b0;

end

end

case不识别x或者z

多谢小编 那我这种情况该怎么办呢?

把你的addr上拉或者下拉

啊偶..谢谢 好主意 可是我的硬件已经做好了,悲剧了,没有上拉或者下拉电阻,我再来想办法换个算法试试 呵呵

不做选择的时候直接赋个无效值不就得了

你的程序里的ADDR值都还是Z,怎么可能能做判断呢。

小编似乎没有理解verilog硬件语义啊?

不要把verilog当成软件代码那样去写!

always@(posedge i_clk or negedge RST)

if(!RST)

xxxxxxxxx

else if(~IS)

case(ADDR)

xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx