关于信号延时的扩展问题,棘手

时间:10-02

整理:3721RD

点击:

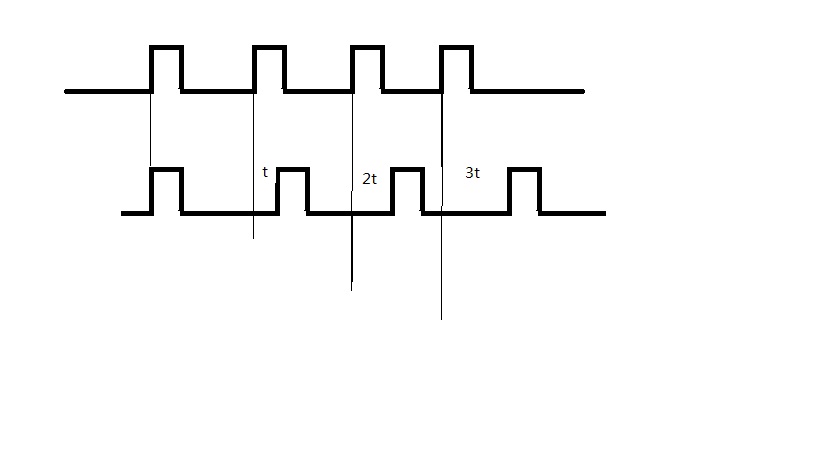

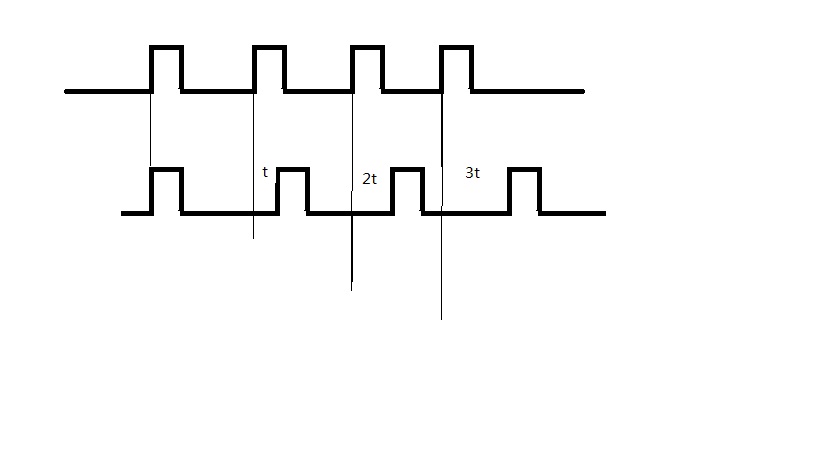

我要用Quartus设计一个周期信号延时模块,实现如下图

信号在周期内,输出信号上升沿比原信号延时t,延时的时间是步进的。想了很久也试了很多,求教各位帮忙。

信号在周期内,输出信号上升沿比原信号延时t,延时的时间是步进的。想了很久也试了很多,求教各位帮忙。

用高频时钟采样,否则不可以做

1、第一个脉冲不延迟 则需要组合逻辑来做

2、以后的脉冲 需要时序电路来做

也就是说你的输出有两个路径,

而且你必须有一个采样时钟,采样时钟还需要与你的输入信号有严密的关系(或则说你的采样时钟产生最上面的那个输入)

如果t不是很小的話,可以用高頻時鐘採樣。如果太小的話,FPGA內部應該有delay單元可以用的。altera的沒用過,用過xilinx的

我想的是用一个时钟,还有一个与主信号相关的复位清零时钟,一起控制计数器,脉宽可以不一样,还有第一个输出不一定没延迟,主要是在步进的思路我理不清,谁能说详细点呢?