FPGA的上电复位?

可以用外部的复位脚引入复位,或用计数器延迟一段时间进行复位。

如果电路中有上电复位信号,可引进来展宽使用;如果没有,可以搭一个RC复位电路引进来展宽使用。

一般FPGA有一个加载成功Done信号,可以用它复位状态机。

1。使用异步复位电路,注意状态机的default和异步复位值在硬件级实现最好是一样,

2。加一个有上拉电阻的输入端口,在去毛刺后延时作为reset

3。内部产生一个reset,以下错误代码只能参考,不能照搬!

reg [7:0] rst_ini ;

reg rst_n ;

wire rst_raw ;

assign rst_raw = 1'b1 ;

always @( negedge clk or negedge rst_raw )

begin

if( ~rst_raw )

begin

rst_ini <= 8'b0000_0000 ;

end

else

begin

rst_ini <= { rst_n[6:0], 1'b1 } ;

end

end

always @( negedge clk or negedge rst_raw )

begin

if( ~rst_raw )

begin

rst_n <= 1'b0 ;

end

else

begin

rst_n <= & rst_ini ;

end

end

多谢上面几位高人的指导,我将认真学习,潜水思考,谢谢!

可以做一個手動按鈕接到FPGA的接腳

按下去時接腳連到ground

就可以達成低電位reset的功能

不知道這樣可以嗎

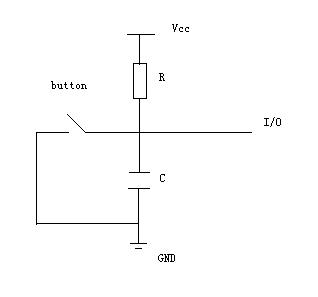

可以将复位按钮和上电自动复位做在一起,只要用一个脚位。

呵呵,这也行?

都行,呵呵

楼上上的那张图行吗?感觉上电的时候没有低电平从IO进去啊?

弱问

当然有用啦。上电的瞬间,电容由于带电量为0,所以两端电压为0,可以通过调整RC数值来调节低电平时间长度。

抱歉啦,我比较弱,当时没太看懂

上网又作一下功课,大概有两点收获:

1. 这个电路容易出错。比如说电源突然中断一下再上电的时候,电容可能还没来得及放电,电源再上电的时候就无法产生正确的复位信号。解决的办法好像是在reset‘节点再放一个二极管到电源,提供一个电源还没上来时的快速放电通道。

2. 我看到的几乎所有的介绍里面都有提到,该电路在上电比较慢的情况下会失效,这个好像是因为上电慢的时候电容充电的速度就能跟上,所以无法产生有效的复位信号。解决的方法是...使用专门的上电复位芯片-___-

一般电路可以用RC电路加二极管,FPGA电路不行的,FPGA上电时要先从FLASH中加载位流,时间约200ms,加载后Done信号为低,表示FPGA开始工作了。一般用Done信号初始化FPGA内部逻辑。

也可以通过约束直接指定状态机寄存器在config之后的值

搭一个RC复位电路引进来展宽使用

FPGA现在用的还是比较多啊,毕竟研发相对容易

好贴,就是需要这样的讨论,学习了!

我最近也在看这个呢

eetopeetopeetopeetop

11

自己可以使用用一个按键,将它做消抖动处理后,作为全局复位,不过这个是复位是要手动的

可以通过上电复位去促发你的程序。也可以外置一个复位按钮去操作。但是这些要看你想实现什么样的功能。

学习了

不错~

好像本身fpga有设定

你的FPGA上电复位时间,要保证在FPGA配置时间长一点。

不然可能会有问题。

当然如果你用的CPLD或者flash工艺的FPGA,就不用考虚这些问题了。

谢谢大家的讨论.学习了.