ISE10.1警告求助

时间:10-02

整理:3721RD

点击:

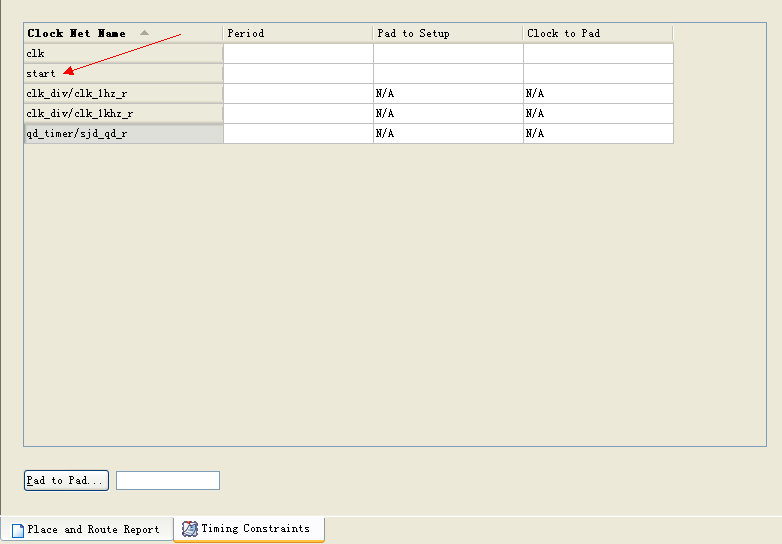

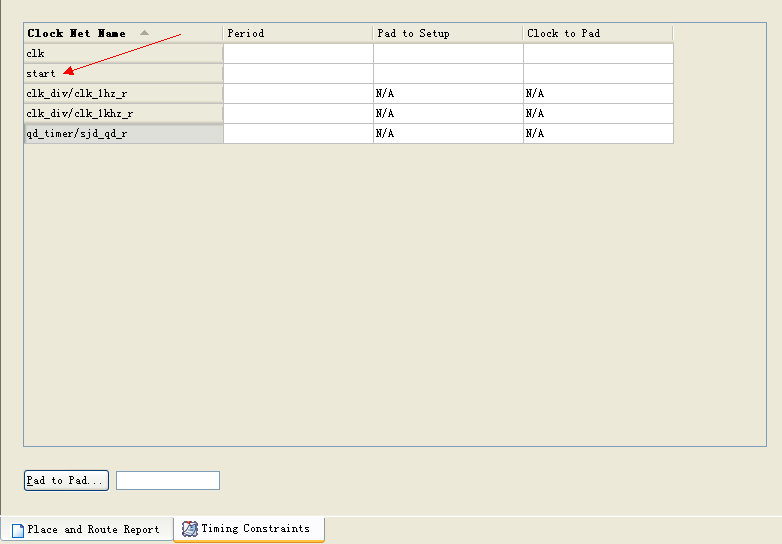

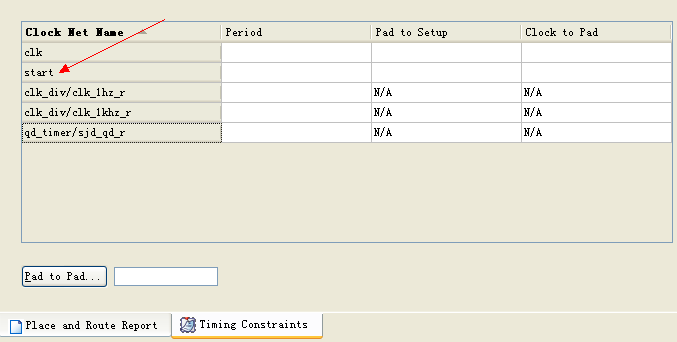

我是新手。最近实验课要做一个设计,用ISE10.1综合下载,用Verilog语言编程,但遇到一个很不解的问题。在设计中,start信号就是一个普通的输入信号,并不是用作时钟,但点开create timing constraints发现软件把start信号当做了时钟,和clk列在一起了。结果就是布线老是通不过,没法生成下载文件。一点都搞不懂了,求高手帮帮忙啊~

布线报告:

ERRORlace:1018 - A clock IOB / clock component pair have been found that are not placed at an optimal clock IOB /

clock site pair. The clock component <start_IBUF_BUFG> is placed at site <BUFGMUX_X1Y1>. The IO component <start> is

placed at site <L6>. This will not allow the use of the fast path between the IO and the Clock buffer. If this sub

optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .ucf file to

demote this message to a WARNING and allow your design to continue. However, the use of this override is highly

discouraged as it may lead to very poor timing results. It is recommended that this error condition be corrected in

the design. A list of all the COMP.PINs used in this clock placement rule is listed below. These examples can be used

directly in the .ucf file to override this clock rule.

< NET "start" CLOCK_DEDICATED_ROUTE = FALSE; >

布线报告:

ERRORlace:1018 - A clock IOB / clock component pair have been found that are not placed at an optimal clock IOB /

clock site pair. The clock component <start_IBUF_BUFG> is placed at site <BUFGMUX_X1Y1>. The IO component <start> is

placed at site <L6>. This will not allow the use of the fast path between the IO and the Clock buffer. If this sub

optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .ucf file to

demote this message to a WARNING and allow your design to continue. However, the use of this override is highly

discouraged as it may lead to very poor timing results. It is recommended that this error condition be corrected in

the design. A list of all the COMP.PINs used in this clock placement rule is listed below. These examples can be used

directly in the .ucf file to override this clock rule.

< NET "start" CLOCK_DEDICATED_ROUTE = FALSE; >

If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .ucf file to demote this message to a WARNING and allow your design to continue.

楼上的做法可以解决这个问题,但是感觉有点舍本逐末,因为根本的没有解决掉。

start_IBUF_BUFG,从这里看,你检查一下start为什么会被认为是clock呢,是否经过了一个IBUFG,这种clock buffer,好好检查一下代码,应该没有问题。

代码与IBUFG怎么对应起来呢?什么样的信号用法会导致IBUFG呢?就是不知道start信号怎么被认为是clk的。你觉得可能是什么原因啊?

你再仔细检查一下代码,看有没有其他地方把start当作时钟信号使用了

1.使用buffer_type属性,强制不使用BUFG

2.检查代码中是否有类似(posedge starta)的写法

我查看了源程序,所有用到start信号的地方,都是if(start)这样的判断语句,没有用到start的边沿。还是没有想明白为什么将start信号判断为时钟信号类型。郁闷