请教下如果寄存器的时钟端用普通信号代替,在DC前端该怎么设置?

always @ (posedge we or posedge rst)

begin

if ( rst )

data <= 8`b0;

else

data <= data_in;

end

其中we信号是个普通的信号,并不是电路的时钟信号,我想在we的上升沿来采集数据,那我在DC设计中该怎么设置?是把we信号当成时钟信号一样处理吗?或者代码有没有别的替代写法?谢谢!

我也遇到这样的问题,哪位大侠能指点一二?

我的理解还是用时钟同步的好

always @ (posedge clk or posedge rst)

begin

if ( rst )

data <= 8`b0;

else if (we == 1)

data <= data_in;

else

end

如果担心时钟采不到we,最好先把we用时钟同步一下不知道理解的对不

看你的WE信号与系统时钟是不是同一个时钟域。如果是的话,在系统时钟域中处理。

不是的话,比系统时钟低则打两拍采沿,比系统时钟高的话,则需要WE信号的保持宽度至少是一个系统clk周期。

回复3楼:我现在担心的不是采不到we,而是采不到data_in。比如clk的周期是30ns,而data_in的保持建立时间才10ns,用clk采的话很难采到,只有用we的上升沿去采才能稳妥的采到,不知道说明白了没有。

尽管不认为你的理解对,如果你只是说DC里面的约束怎么写,用generated clock

从主时钟派生出你的we时钟,并设定时钟之间的相位差(延时)

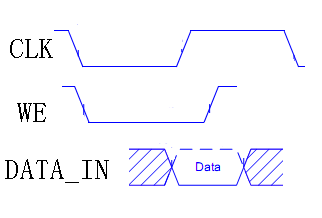

请教下该怎么理解才对?我以前是在clk的上升沿然后用we信号的低电平去写data_in的,但是发现如果按照data_sheet上的极限要求的话很可能clk的上升沿还没来,data_in数据已经没了,附图如下。请问我除了用we信号的上升沿去采data_in数据,还有别的方法吗?谢谢指教!

或者这样,比如clk的周期是30ns,而data_in的保持建立时间最小为10ns。

在同步电路里面出现了使用逻辑信号当时钟就是个问题。

我不准备说任何关于为什么不合适的话

如果你觉得必须这么做,做下去好了。大家都是这么过来的。

不知道,来学习,似乎最好用时钟来采,否则后续timing问题很多的~~

寄存器的CK端一般是不允许使用数据的,原因是破坏了同步设计,使得整个设计无法做时序分析了。

时钟原本是一个独立的专用的网络,时序分析时钟周期作为参考的。

如果以数据信号作为时钟,那么就不容易分析该信号作为数据时的时序了。

因此不建议讲WE作为时钟使用。

从你说的情况,clk是不是data_in信号的随路时钟,如果是就不该出现偏差那么大的,否则就是板级布线问题。

WE信号是写使能还是数据有效信号,如果类似总线控制写使能作用,那么该电路应该是一个异步总线接口。

小编,最好能讲情况说仔细点,方便大家一起讨论分析。