关于时序仿真问题,请高手解答

时间:10-02

整理:3721RD

点击:

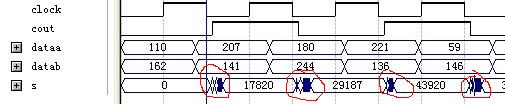

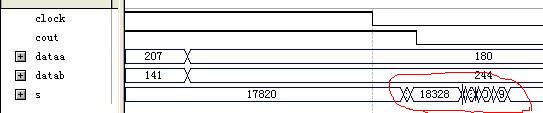

请问在时序仿真时出现如图红圈所示的数据是为什么?怎么避免?如果没有这些数据,则逻辑全部正确。还有在QUARTUS2中如何进行时序约束?请高手帮忙,谢谢

是各个位信号改变的时间不完全一致造成,时钟应在信号稳定时间采样

2# xqylyq

谢谢你,

那么请问 如何让时钟在信号稳定时间采样?

是不是设置时钟信号的建立时间和保持时间,是的话,应该依据什么规定这些时间?

时序约束的规定,没有统一的,要看你的时钟频率和设计要求来定,当然也需要考虑外部的电路。在时序仿真中,经常出现这种变化,是很正常的,因为每个信号经历的路径延时不同,但一般不会很大。要是对于高速设计来说,就要对时序严格要求了。

4# gaurson

谢谢!

好的,很好,从问题中借鉴了一些东东

因为各条路经延迟不一样,当这些路径汇集到一个点的时候,就会产生如图的glitch,貌似这个逻辑的最后用了一个低通的latch,显然clock低电平来得太早,在glitch出现的时候,latch是透明的,导致glitch传播到了output,为了避免输出的glitch,需要适当的延迟clock的下降沿,或者整体延时一下。 另外,可以调整逻辑设计,避免这种路径延迟不平衡的状况,还可以通过优化关键路径,来使glitch出现的时间提前。

不错~最近也遇到类似的问题

QUARTUS2中进行时序约束,用TimeQuset。