讨论电路除噪的方法

几个触发器对输入信号串行移位,然后若触发器的值全为1时使输出为1,若全为0时输出为0,其余保持。

有次面试,有人说这种方法需要更快的时钟,可以用组合逻辑除噪,本人百思不得其解。

大家有什么好思想,拿出来分享下呗!

为啥没人留言呢,讨论一下吗!

小编可否科普一下电路除噪的来历与现象?

科普是啥意思?楼上啥意思,没明白!

合逻辑除噪更不能消除吧,消除噪声要用时序电路

科普就是用简单通俗易懂的语言来把“电路除噪的来历与现象”给我讲清楚,好吗?

因为我还是不怎么清楚你究竟想达到什么目的,所以也就不敢乱说了。

奥,这么会是啊

比如,做一款芯片,需要对外部输入的大约24k的信号进行边沿检测,进行检测的始终大约为20M,如果在24k的信号上面产生一个持续时间大约1/20m 的毛刺,那这个边沿检测就会产生一个错误的输出,所以进行边沿检测的之前就必须除噪,这里我觉得可以用几个触发器进行除噪,这样还可以达到同步的目的。

可是如果没有这个更快的时钟呢,比如一个外部输入的时钟,上面有毛刺,你的设计里面仅有这一个时钟,那如何除噪呢?

我想如果只有这一个时钟的话,就只能用组合逻辑来除噪了!

为啥论坛中说毛刺的都是芯片内部自己产生的,若是外部输入的信号有毛刺呢,就是所谓的噪声,怎么滤除呢,如果没有更高频率的时钟的话?

哦,樓主的意思我看明白了。只不過我也想不出來怎麽能通過組合邏輯來去除毛刺。對於芯片閒的信號方面經驗不足。

感覺芯片閒的信號如果有毛刺的話,應該屬於高頻信號,那麽應該用低通模擬濾波器就可以去除吧。其實你先前的辦法也可以説是一種數字濾波器吧。

對於濾波器電路我也不怎麽熟悉,不知道說的對不對。

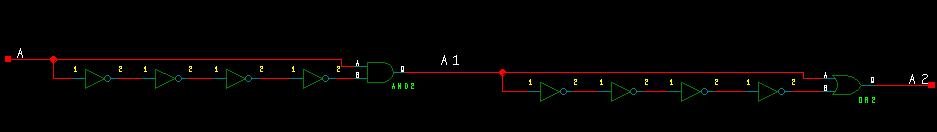

a input

delay line : a_delay

消除上跳 a & a_delay

消除下跳 a | a_delay, 对于高频干扰有效

以前没有太多了解,现在开始关注了。

谢谢

原来是这么处理啊,但是这么做有一个前提就是要预先知道噪声只有向上的毛刺或者只有向下的毛刺,是吗?

学习学习

我能明白你的意思,相当用几个缓冲器将信号延迟一段时间,然后与原来的信号比较,我也想过这个办法,可是怎样得到一个最终的电路呢

,虽然每条语句都可单独消除上跳或下调,那需要都消除呢,怎么组合?这个我没想通?

向上向下的毛刺有办法确定吗?

有意思。

个人认为要是都要消除的话,等于是(a & a_delay)&(a | a_delay),但随之而来的就是clk的jitter问题,要用严格的时序约束来让这两路data path等延时才行。

我的意思是说,除非是我们在做之前就知道了这个输入信号只有向上的毛刺,或者只有向下的毛刺,那么可以用这种方法来解决。

但是如果信号这两种毛刺都有的话,那就没辙了。

至于如何来确定只有向上的毛刺还是只有向下的毛刺,就只能通过示波器了吧?

我对你的这个算式持有异议,我刚才画了波形按照你的算式做了一下,发现向下的毛刺是无法消除的。你可以自己画画看。

学习……

XUEXIZHONG

肯定不是简单的让这两个信号相与,我曾试过异或,同或,与,或,等等,或者两个信号的同或作为信号输入的使能,可是时序就会有问题了,就怕外边没毛刺,反倒自己产生了毛刺!

继续等待大家讨论!

谢谢捧场!

当时没仔细考虑,确实有问题。

还有个思路:

输入 clk,

延迟一次 clk_d1,

clk_2=clk&clk_d1,

再将clk_2延迟一次,得到clk_d2,

最后clk_o=clk_2|clk_d2.

其实现还是有一些时序限制。

上跳下跳级联 即可消除上下跳

传个图 ,表达一下

高高高,牛人啊,哈哈,解决了,恩,没想到!

组合电路除噪解决了,呵呵

解决了,呵呵

谢谢你给的方法,非常感谢,受教了,呵呵!

这个思路很有意思,学习了