如何用VHDL或Verilog最简洁地描述出一种逻辑功能(详见正文)

如果a产生了一个时钟周期的脉冲,那么b则输出一个长达2或3个时钟周期的脉冲(即产生一个脉冲展宽的信号)

要求不能用计数器实现(我感觉用计数器来描述代码还是有点多,我想应该有更简洁的描述)

这个相当于分频啊

不用计数器

always @(posedge clk)

clkout<=clkout +1;

二分频,不用计数器

其实现实中你这样没必要

现在芯片资源越来越多,价格越来越低

只要设计出的东西ok就行了

2# wyqkiss

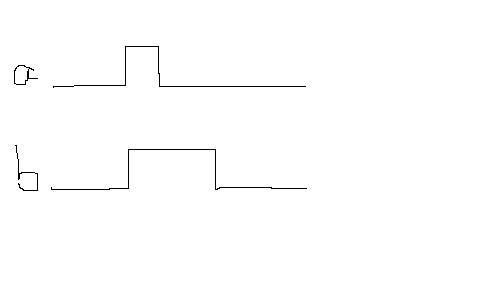

谢谢!其实不是分频。a不是一个时钟信号,而是一个单脉冲信号,正脉宽为一个时钟周期。这个信号产生后,我希望输出一个新的单脉冲信号b,b的正脉宽为2到3个时钟周期。逻辑图如下(时钟信号未画出):

有一点没有明确 a与clk的相位关系

RS 触发器可解决

a作为set

被时钟延迟后的a作为clr

不知道这样是否满足你的要求

单脉冲信号宽度为一个时钟周期,这样在时钟下一定能被打到

将这个单脉冲信号寄存一拍,若原信号为pulse,寄存后的信号为pulse_d,将这两个信号或上pulse^pulse_d,即扩展为两个时钟周期宽度

process(clk) begin

if clk'event andclk = '1' then

a1 <= a;

a2 <= a1;

a3 <= a2;

end if;

end process;

b= a or a1 or a2 or a3 ;

module pulse_modulate();

reg clk;

reg pulse;

reg rst_n;

wire pulse_out;

initial begin

clk <= 0;

pulse <= 0;

forever #5 clk <= ~clk;

end

initial begin

rst_n <= 0;

#100 rst_n <= 1;

end

always begin

repeat(5)

@(posedge clk);

pulse <= 1;

@(posedge clk);

pulse <= 0;

end

pulse p1(

.clk(clk),

.rst_n(rst_n),

.pulse_in(pulse),

.pulse_out(pulse_out)

);

endmodule

module pulse(

input clk,

input rst_n,

input pulse_in,

output pulse_out

);

reg [ 2: 0] shift;

always@(posedge clk or negedge rst_n) begin

if (~rst_n) shift <= 0;

else if (pulse_in) shift <= 3'b111;

else shift <= {1'b0,shift[2:1]};

end

assign pulse_out = shift[0];

endmodule

很多方法啊 A延迟一拍再做逻辑

5# sirius.yuan

谢谢。是个好方法。

6# wasabi55

谢谢。很简洁的代码

7# lokta

这个思路好啊,我怎么没想到。连测试程序都写出来了,谢谢啦

学习了!

assign b=(| c);

always @ (posedge clk)

begin

c[0]<=a;

c[2:1]<=c[1:0];

end

学习了~

学习

always@(posedge clock)

begin

a_dly[1:0] <= {a_dly[1],a};

end

assign b= a | (|a_dly[1:0]);

6楼正解。

嗯 代码不错