FPGA设计,请教三角滤波器设计相关问题

时间:10-02

整理:3721RD

点击:

对于8kHz采样频率128点FFr变换,频率分辨率为8000/

128=62.5。具体计算时可在PC机上用滤波器组的中心频率

除以分辨率,事先求出其对应FFT频谱中的第几点。根据式

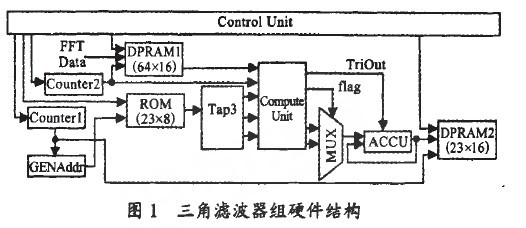

(2)计算每组三角滤波器的输出。具体硬件结构如图l所示。

其中ROM保存了23组三角滤波器中心频率的对应点,

DPRAMI保存了一帧FFT变换的结果,DPRAM2保存23组滤

波器组输出结果。Counter2是模64的计数器,用来记录FFT

频谱对应点,Counterl是模23的计数器,用来记录当前滤波器

编号。该结构工作原理是:ROM连续输出3个数据(对应于一

个滤波器的下限、中心和上限频率),由深度为3的Tap3锁存,

ComputeUnit比较当前FFT频谱点与当前三角滤波器的下限,

中心,上限频率对应点,flag为“lO”计算当前三角滤波器的上

三角输出,为“Ol”计算当前三角滤波器的下三角输出,为“ll”

进入下一个三角滤波器,Counterl加1,并通过MUX选择累加

的数据。ACCU为累加器,将当前滤波器输出累加,Counterl

增加到22时,23组滤波器的输出都保存到DPRAM2中。

请问哪个大人能给点设计思路,或者有过相关经验的可以加qq1067774890

那个control unit 可能是个状态机,具体我也搞不清。就是我想请问下,这个图能不能在quartus里面做出来,用硬件描述语言。这个只是硬件结构,不是电路图,直接把我茫然了。不知道从哪里下手开始设计。

所有的设计你都要先搞明白它的工作原理。然后工作的时序或者数据流向。再细化成一个个的功能模块。再组装这些模块。如果你连原理都没明白还怎么做?

学习学习