高手指点下,入门新手关于modelsim的问题

时间:10-02

整理:3721RD

点击:

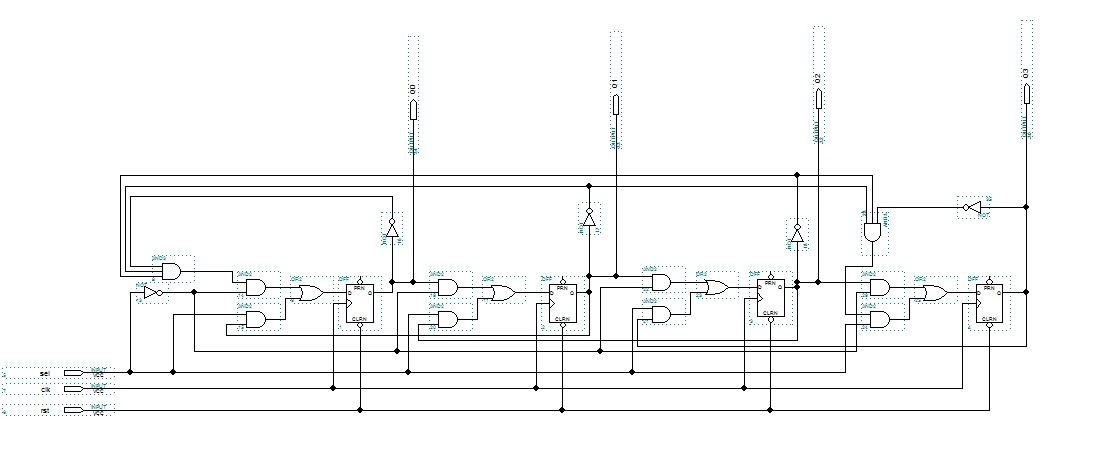

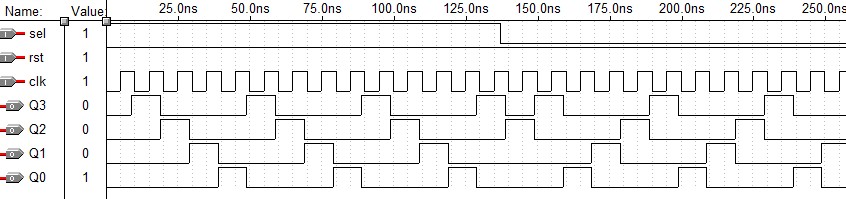

才开始学习verilog,是个双向4位环形计数器,电路图如下,仿真后能实现,可是根据电路图写出门级verilog程序后,在modelsim里功能仿真,输出一直是高租,请高手指导下。

module Four_bits_r_bidir_counter(Q0,Q1,Q2,Q3,Q0_b,Q1_b,Q2_b,Q3_b,sel,clk,rst);

output Q0,Q1,Q2,Q3,Q0_b,Q1_b,Q2_b,Q3_b;

input sel,clk,rst;

wire Q_forw,Q1,Q2,Q_back;

and (Q_forw,Q0_b,Q1_b,Q2_b);

and (Q_back,Q1_b,Q2_b,Q3_b);

begin

Sel_manner M0(D0,sel,Q_forw,Q1);

Sel_manner M1(D1,sel,Q0,Q2);

Sel_manner M2(D2,sel,Q1,Q3);

Sel_manner M3(D3,sel,Q2,Q_back);

Dflipflop DFF0(Q0,Q0_b,D0,clk,rst);

Dflipflop DFF1(Q1,Q1_b,D1,clk,rst);

Dflipflop DFF2(Q2,Q2_b,D2,clk,rst);

Dflipflop DFF3(Q3,Q3_b,D3,clk,rst);

end

endmodule

module Sel_manner(D,sel,Q_forw,Q_back);

output D;

input sel,Q_forw,Q_back;

wire w1,w2;

and (w1,Q_forw,~sel);

and (w2,Q_back,sel);

or(D,w1,w2);

endmodule

module Dflipflop(Q,Q_b,D,clk,rst);

output Q,Q_b;

input D,clk,rst;

wire nan1,nan2,nan3,nan4;

nand(Q,Q_b,nan4);

nand(Q_b,rst,nan2,Q);

nand(nan2,clk,nan1,nan4);

nand(nan4,clk,nan3,rst);

nand(nan1,nan2,rst,D);

nand(nan3,nan1,nan4);

endmodule

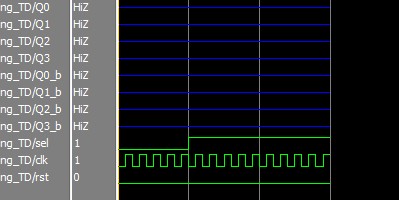

testbentch如下:

module Four_bits_ring_TD();

wire Q0,Q1,Q2,Q3,Q0_b,Q1_b,Q2_b,Q3_b;

reg sel,clk,rst;

parameter Period = 20;

initial

begin clk=0;

forever #(Period/2) clk=~clk;

end

initial

begin

rst=0;sel=0;

#30 rst=1; sel=0;

#15 rst=1;

#100 sel=1;

end

initial #300 $finish;

endmodule

module Four_bits_r_bidir_counter(Q0,Q1,Q2,Q3,Q0_b,Q1_b,Q2_b,Q3_b,sel,clk,rst);

output Q0,Q1,Q2,Q3,Q0_b,Q1_b,Q2_b,Q3_b;

input sel,clk,rst;

wire Q_forw,Q1,Q2,Q_back;

and (Q_forw,Q0_b,Q1_b,Q2_b);

and (Q_back,Q1_b,Q2_b,Q3_b);

begin

Sel_manner M0(D0,sel,Q_forw,Q1);

Sel_manner M1(D1,sel,Q0,Q2);

Sel_manner M2(D2,sel,Q1,Q3);

Sel_manner M3(D3,sel,Q2,Q_back);

Dflipflop DFF0(Q0,Q0_b,D0,clk,rst);

Dflipflop DFF1(Q1,Q1_b,D1,clk,rst);

Dflipflop DFF2(Q2,Q2_b,D2,clk,rst);

Dflipflop DFF3(Q3,Q3_b,D3,clk,rst);

end

endmodule

module Sel_manner(D,sel,Q_forw,Q_back);

output D;

input sel,Q_forw,Q_back;

wire w1,w2;

and (w1,Q_forw,~sel);

and (w2,Q_back,sel);

or(D,w1,w2);

endmodule

module Dflipflop(Q,Q_b,D,clk,rst);

output Q,Q_b;

input D,clk,rst;

wire nan1,nan2,nan3,nan4;

nand(Q,Q_b,nan4);

nand(Q_b,rst,nan2,Q);

nand(nan2,clk,nan1,nan4);

nand(nan4,clk,nan3,rst);

nand(nan1,nan2,rst,D);

nand(nan3,nan1,nan4);

endmodule

testbentch如下:

module Four_bits_ring_TD();

wire Q0,Q1,Q2,Q3,Q0_b,Q1_b,Q2_b,Q3_b;

reg sel,clk,rst;

parameter Period = 20;

initial

begin clk=0;

forever #(Period/2) clk=~clk;

end

initial

begin

rst=0;sel=0;

#30 rst=1; sel=0;

#15 rst=1;

#100 sel=1;

end

initial #300 $finish;

endmodule

testbanch 中没有例化好好看看书上例子

顶楼上的

呵呵,这样的不要在这一业混了,大学毕业做鸭赚的钱也比你学的这样的水平赚的多.实在不可以毕业后当兵去吧.

楼上的,你智商高了点,但道德不行

刚学嘛,犯点错也是必然的,重要的能吸取教训,以后真正做项目的时候就不要犯这种错误了,会被人鄙视的 呵呵