请教,关于spartan-3a slice的利用率问题

时间:10-02

整理:3721RD

点击:

最近把一个Cyclone II下的项目移植到Spartan-3a上

Cyclone II用的是ep2c8 8k的LE用了85%

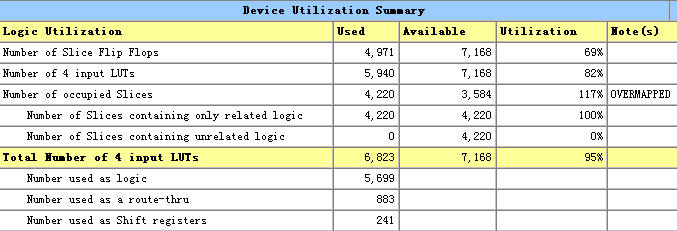

spartan-3a 用的xc3s400a 也是8k的LE的样子,结果slice占用率到了120%!

LUT和FF本身的占用率都在70%上下 郁闷 怎么设置都没有办法把slice的利用率提高

感觉低端片子xilinx的实在是没有Altera的好用

这资源利用率也比Cyclone II的差得太远了,是我不会设置的原因吗?

有没有高手指导一下 这个问题该怎么解决?非常感谢

补充一下:

unrelated logci始终是0

试一下面积优先的选项

把layout以后的report贴出来 大家帮我看下还能优化么?

不是都说related logci满了以后 就会使用unrelated logic吗 为什么总是0?

这要看你的程式了,同性能的FPGA一定是性能互换的,只是资源的用法可能不同,不过你的芯片资源用到85%是不建军议这样用的.

我就郁闷为什么cp2c8也是8k LE 就能放下(85%)

xc3s400a就不行呢。

优化代码,不要指望工具,slice的使用效率太低

可不可以这样理解

spartan-3 的1slice 包含2lut 2dff的结构 其实并不如

cyclone2 1LE 包含1lut 1dff 的结构的利用率高?

不然这如何解释。

另外 unrelated logic 的利用率总是0% 这个很奇怪

xilinx的官方文档也乱七八糟 查来查去找不到解决办法

急 自己顶一下

恩,这个倒是可以解释为什么Altera的低端干得过Xilinx