请问IDE(ATA)硬盘引脚的逻辑电平是多少?

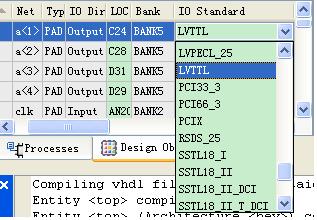

电平的定义在协议第4章有讲的,应该归于5V TTL一类。对于FPGA来说,将其IO类型设成LVTTL或LVCMOS33在电平协议上都是能满足要求的,但是这款FPGA不能兼容5V输入,5V的信号输入有可能对其造成损坏,最好在外面加能承受5V输入的接口芯片转换一下。

2# mj1029

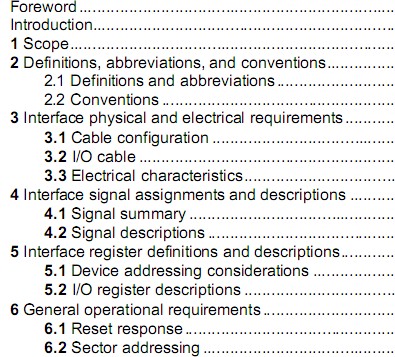

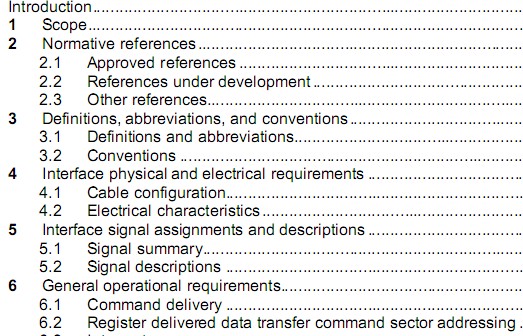

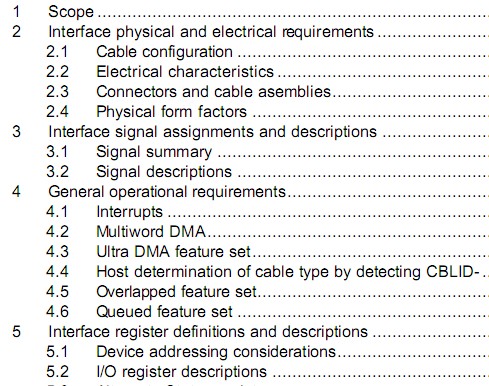

你用过IDE的协议吗?不知道你看到协议是什么版本,好几个协议的第四章都没有啊:

ATAPI-3:

ATAPI-5:

ATAPI-7:

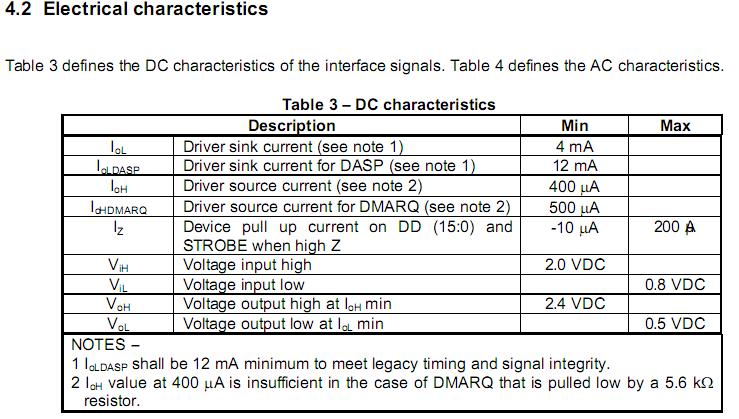

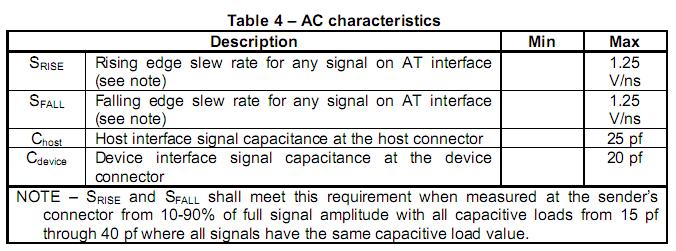

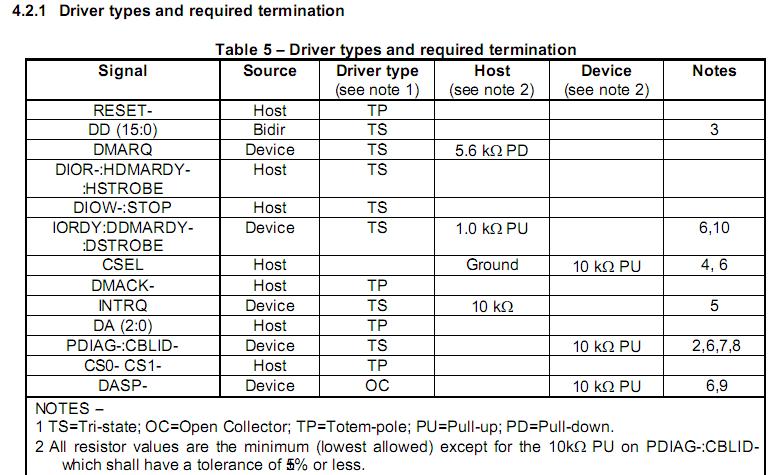

atapi-5中的第四章倒是有个electric characteristics,不过里面讲的看不太懂:

上面的Table3不就是你要的东西吗?输入电压>2V,表示逻辑1,电压<0.8V,表示逻辑0;而输出逻辑1时,电压>2.4V,逻辑0时,电压<0.5V。这就是TTL电平的规定值,你查一下FPGA的LVTTL电平定义是不是也是这样的?

你是不是要做一个SD卡控制器啊

5# mj1029

我是要开发一个硬盘接口控制器。查了一下电平标准:

TTL:

Vcc:5V;VOH>=2.4V;VOL<=0.5V;VIH>=2V;VIL<=0.8V。

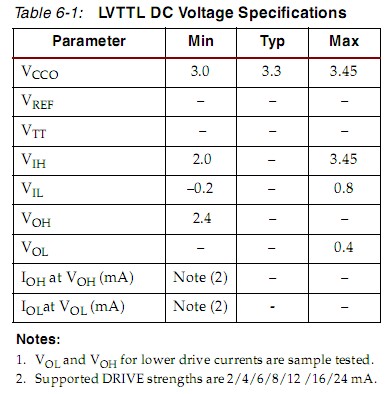

3.3V LVTTL:

Vcc:3.3V;VOH>=2.4V;VOL<=0.4V;VIH>=2V;VIL<=0.8V。

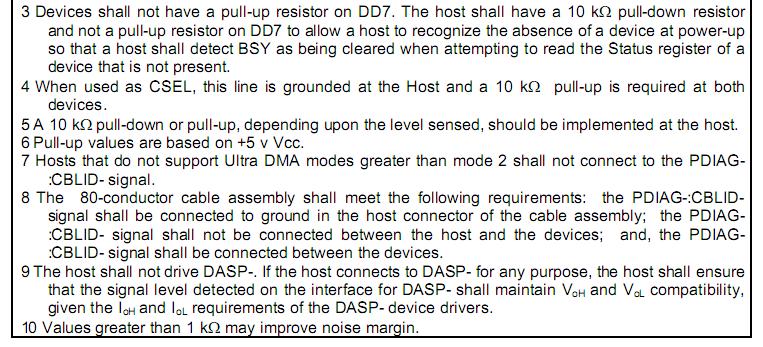

LVTTL逻辑电平标准的输入输出电平与5V TTL逻辑电平标准的输入输出电平很接近,但是在v4系列芯片中,LVTTL逻辑支持的最大输入高电平是3.45v(见下图)

看来我只有再做个转接板了。我程序调了段时间没什么结果,不知道是不是这个原因。也不知道FPGA芯片是不是已经损坏了,有没有什么好的方法做下测试啊?

加我QQ277971459.我也正在做这方面的东西,可以交流一下撒