q2生成的pll输出时钟为什么有不应该的相位差?

时间:10-02

整理:3721RD

点击:

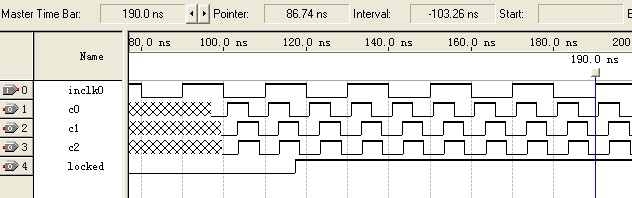

我用q2的core做了个锁相环,输入时钟50兆,输出三路皆为100兆的时钟,相移参数我都设成了10ns,然而仿真出来的图却有一路与另外两路时钟相位不一致,如图1所示,请问这是为什么呢?

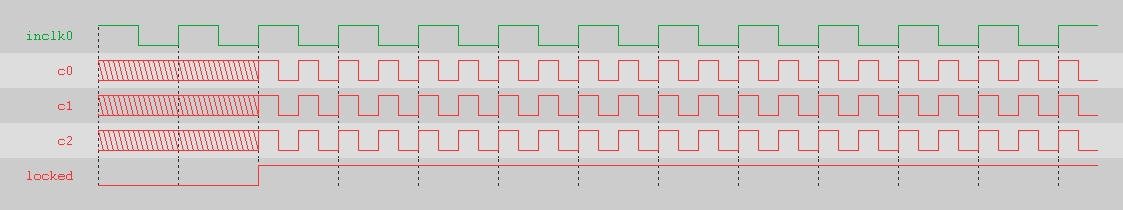

(生成pll时我选择了生成一个仿真图文件,这个图的输出关系却是正确的,如图2)

(生成pll时我选择了生成一个仿真图文件,这个图的输出关系却是正确的,如图2)

图1

图2

THE SAME QUESTION

100M就是10ns,相移10ns干嘛呢?

3# wasabi55

就是不加相移结果也一样啊