为何延时减少了?

时间:10-02

整理:3721RD

点击:

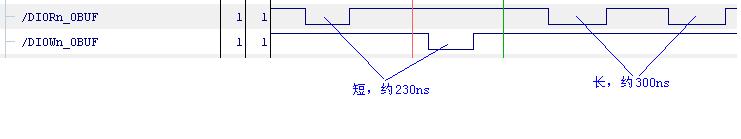

我做一个接口的时序,用chipscope抓取的图如下:

图中的DIORn和DIOWn两个信号的低电平持续时间是用同一个计数器模块来实现的,给的计数器的参数相同(即计数时长相等)。我设置的延时大概是300ns左右,做功能仿真时各段低电平保持时间都满足条件,然而综合实现后烧到FPGA中,用chipscope观察,左边的两段低电平持续时间却只有230ns左右了。按理说加上寄存器、布局布线等延时后低电平的持续期应该大于等于300ns才对啊,怎么会比300ns小呢?!

是否与综合设置和综合器有关?因为我每综合一次后低电平变短的位置有可能不同了,我用的是ISE自带的综合器

图中的DIORn和DIOWn两个信号的低电平持续时间是用同一个计数器模块来实现的,给的计数器的参数相同(即计数时长相等)。我设置的延时大概是300ns左右,做功能仿真时各段低电平保持时间都满足条件,然而综合实现后烧到FPGA中,用chipscope观察,左边的两段低电平持续时间却只有230ns左右了。按理说加上寄存器、布局布线等延时后低电平的持续期应该大于等于300ns才对啊,怎么会比300ns小呢?!

是否与综合设置和综合器有关?因为我每综合一次后低电平变短的位置有可能不同了,我用的是ISE自带的综合器

chipscope的采样时钟是多少?

2# pptiger

是系统时钟吧?100M的

那个后面的长约300ns的延迟是怎么出来的?和前面的短延迟机制一样吗?

这就很奇怪了,居然相差7个时钟周期?我最开始还有点怀疑是组合逻辑引起的,看来不是。LZ可能的话,把代码贴上来吧。

4# williamloo

用的是相同的计数器模块实现的

ghfhfgjfgjfgjfg

不太明白您的意思。我的程序都是在一块FPGA里跑的。chipscope不也是在FPGA里插入一个核,用内部的ram资源来存储观察信号吗?您的意思是否是最好将chipscope的ILA核放另一块FPGA里?