麻烦各路高手不吝赐教!有关门控时钟和行波时钟

我的设计中做了一个分频器,时钟分频后送输出管脚,其它硬件电路送时钟,但是在分频器编译过程中说产生了门控时钟或着行波时钟,

我查资料说,门控时钟影响系统稳定性,前级分频不能做后级的时钟,但是我的分频是直接输出了,

请问我这样做,如果不对这个门控时钟处理的话,会不会影响系统可靠性呢?

设计是采用altera的EP2C8T144,开发环境Q7.0,目的是输入时钟12M,锁相环倍频后24M,在通过计数器产生CCD所需各种时序,送给AD的像元时钟DATACLK,该时钟为1M,在分频过程中产生了门控时钟。

补充:

下面DATACLK产生代码,两个计数器cnt_1M和cnt_LS都是通过24M分频至8M(采用时钟使能设计),再通过8M计数产生。

DATACLKS:process(clk24M,rst_state)

begin

if clk24M'event and clk24M='1' then

if rst_state='0' then

DATACLK<='0';

else

if MODE="00" then

if ((cnt_total>="0000000000000") and (cnt_total<"0000000000000"+1120)) then

DATACLK<='1';

elsif cnt_1M="000" or cnt_1M="001" or cnt_1M="010" or cnt_1M="011" then

DATACLK<='0';

else

DATACLK<='1';

end if;

elsif MODE="01" then

if ((cnt_total>="0000000000000") and (cnt_total<"0000000000000"+880)) then

DATACLK<='0';

elsif cnt_LS="1100" or cnt_LS="1101" or cnt_LS="1110" or cnt_LS="1111" then

DATACLK<='1';

else

DATACLK<='0';

end if;

elsif MODE="10" then

if ((cnt_total>="00000000000000") and (cnt_total<"00000000000000"+1640)) then

DATACLK<='1';

elsif cnt_1M="000" or cnt_1M="001" or cnt_1M="010" or cnt_1M="011" then

DATACLK<='0';

else

DATACLK<='1';

end if;

elsif MODE="11" then

if ((cnt_total>="00000000000000") and (cnt_total<"00000000000000"+1840)) then

DATACLK<='0';

elsif cnt_LS="1100" or cnt_LS="1101" or cnt_LS="1110" or cnt_LS="1111" then

DATACLK<='1';

else

DATACLK<='0';

end if;

end if;

end if;

end if;

end process DATACLKS;

这是warning:Warning: Found 1 node(s) in clock paths which may be acting as ripple and/or gated clocks -- node(s) analyzed as buffer(s) resulting in clock skew

Info: Detected ripple clock "CCD_Driver:inst|DATACLK" as buffer

我也很水,只会verilog,

弱弱的问一句, 你以上的条件表达式中的条件判断‘=’表示相等还是赋值?

我知道verilog是‘==’

“=”是相等的意思,信号赋值用<=,变量赋值用:=

分频后的信号在综合时不走全局时钟网络,只会把它当成信号来处理,如果用作时钟的话就会产生时钟歪斜。

一般不要用自己写的分频程序产生的信号作为其它模块的时钟。

你的频率不是很高,可以先不管警告,直接调试看看。

如果要解决这个问题你可以用PLL模块做,如果没有(如一些CPLD)就用时钟使能方式实现吧。

您好!

我的分频后的时钟直接送到输出脚了,而没有钟控其它模块,请问这样的话,也会影响系统的可靠性吗?

不是时钟怎么会报时钟的warning,你再看看电路图中的那条路径呢?

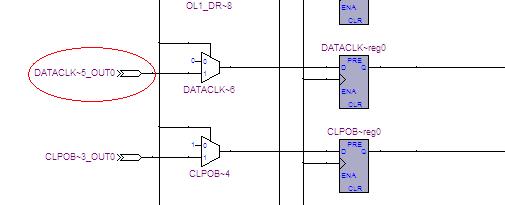

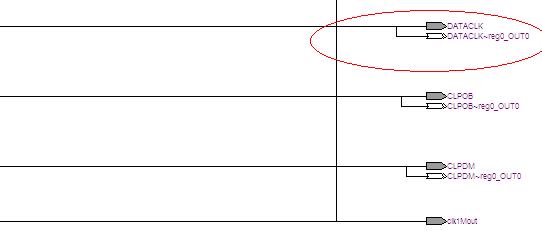

这是有关DATACLK走线的RTL图,两张图左右拼接就行了,

rf

该图接上图左侧

上图的触发器ENA端接的是总时钟24M

分频之后加一级锁存,用最高的频率做锁存时钟

用12M锁相,生成24M,再分频后得到的1M,去片外做AD的CLK,那么该信号无疑必须输出至管脚。

建议将该1M经过1级锁存后,再输出至管脚,用24M做锁存时钟。

多谢各位,是我看错了,DATACLK又返回来,做了异步fifo的读时钟了,

1M应该没问题吧,也必须加锁存器吗?

直接分频出来的信号可以作为其他模块的clk,但是专业些就用锁相环,比较稳定。你后面可以不用锁存器,系统应该比较稳定

多谢各位指教!

我的门控时钟问题解决了,但是又有了新麻烦,

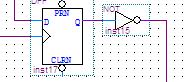

图片是我加的一个dff,时钟端用全局时钟24M,D端接计数器分频出来的1M的DATACLK时钟,Q端过一个非门,接异步fifo的读时钟wrclk。

门控时钟的警告没了,但是又有了新的警告:

Warning: Found invalid timing assignments -- see Ignored Timing Assignments report for details

但是timing analyzing report里还没有红色警告,为何 为何 为啥呀?