请教Modelsim仿真问题,很急!

小弟在用Modelsim SE 6.2b版本做仿真,我现在有两个文件,一个源文件top.v,一个top_test.v测

试文件。步骤是这样的,先在Modelsim下新建文件夹test,将top.v和top_test.v放入其中;第二步是编

译这两个文件,编译正确;第三步是在Library下的work库看到这两个编译好的文件top.v和top_test.v;

第四步是点住这两个文件,点右键选Simulate,出现了sim框,在sim框中也看到这两个文件,但点测试文

件top_test.v的时候,却没有在objects窗口(也就是以前的Signal窗口)中看到任何信号,这样就无法

在wave窗口中加信号了,仿真也就跑不了了。但点源文件top.v则在objects窗口出现信号,但却没有激励

,还是没法跑仿真。请问这是怎么回事?

顺便说一下,top.v和top_test.v在Xilinx ISE10.1下用自带的仿真器是可以跑仿真的,从ISE10.1启

动modelsim se来跑也是可以跑通的,就是在启动modelsim自己加top.v和top_test.v文件时没法跑,自己

在modelsim的环境下从新照抄这两个文件,建立项目来跑都出现上面说的问题,请高手告诉我这是怎么回

事?

两个文件都编译过后,只要点最顶层的模块仿真就可以啦。wave中的信号要自己加,激励要自己写。书上都有说怎么做的

关掉“Enable Optimization”即可。

guoyu

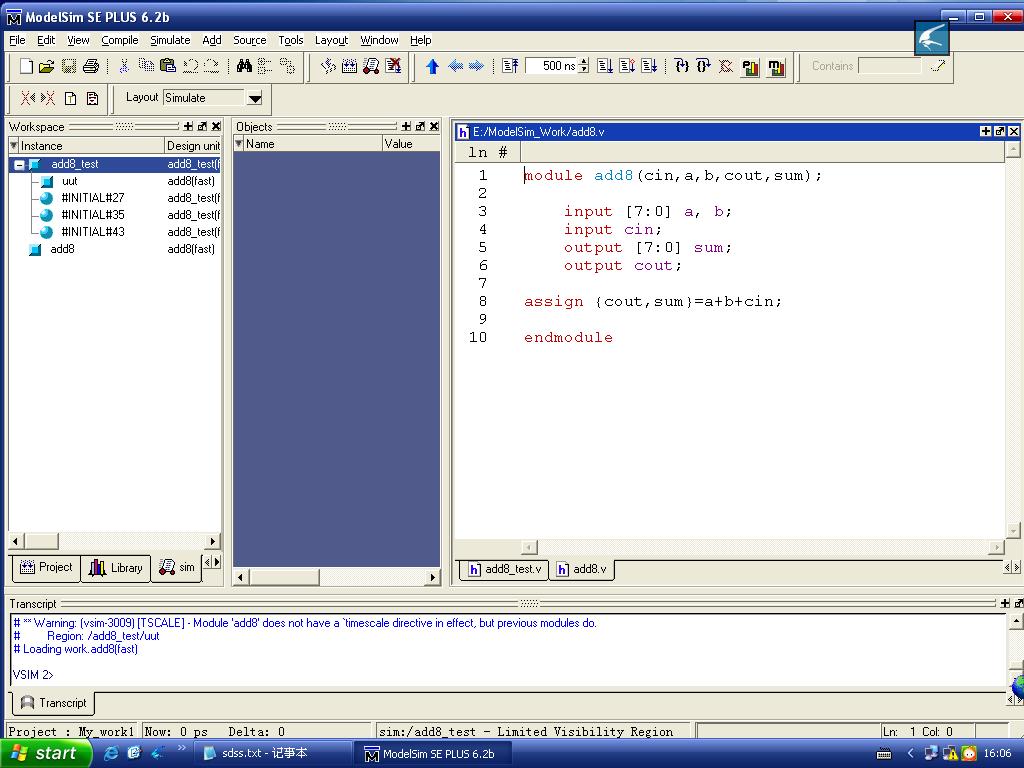

你好,我照你的方法做,还是没有信号,现在付上图片,add8_test.v为测试add8.v的测试文件,右图为模

块add8.v的源文件,一个简单的8位加法器,可是add8_test.v却没有在object中显示信号,请问这是怎么

回事?

下面付上add8_test.v的源代码:

`timescale 1ns/1ps

module add8_test;

reg [7:0] a,b;

reg cin;

wire [7:0] sum;

wire cout;

integer i,j;

add8 uut(.cin(cin),

.a(a),

.b(b),

.cout(cout),

.sum(sum));

initial

begin

a=0;

b=0;

cin=0;

end

initial

begin

for(i=1;i<20;i=i+1)

#10 a=i;

end

initial

begin

for(j=1;j<20;j=j+1)

#10 b=j;

end

initial

begin

$monitor($time,,,,,,"%d+%d+%b={%b,%d}",a,b,cin,cout,sum);

#300 $finish;

end

endmodule

是不是需要ADD?

你的这个代码很简单,其他的问题应该没有,我也认为在仿真时把下面的这个选项“Enable Optimization”,打勾去掉就行了,你在试一下~~~

你 这个情况,以前我也遇到过。好像就是在进行仿真时 ,选中测试文件后去掉Enable Optimization的钩就好了!

问题已经解决,就是把Enable Optimization去掉即可。