我写的一个8位计数器,请高手拍砖与指点!

时间:10-02

整理:3721RD

点击:

我写的一个8位计数器,请高手拍砖与指点!

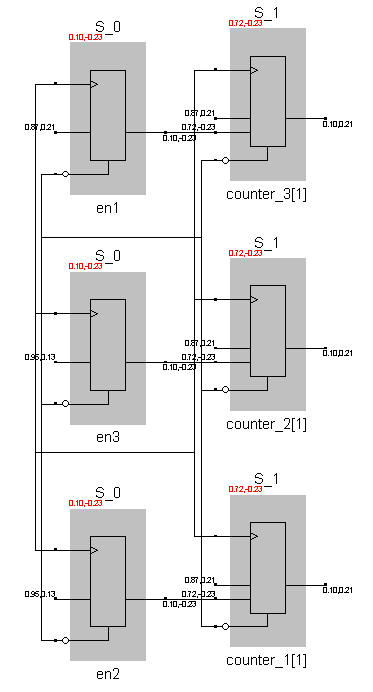

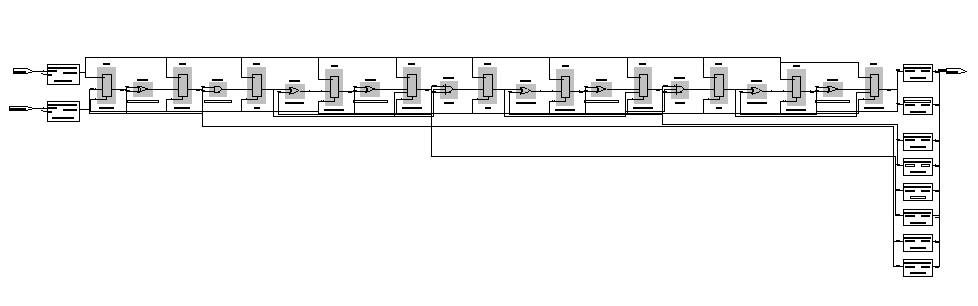

module chaoqian(

i_Clock,

i_Reset_n,

cnt

);

input i_Clock;

input i_Reset_n;

output [7:0]cnt;

reg [7:0]counter;

reg en1;

reg en2;

reg en3;

assign cnt=counter;

always @(posedge i_Clock or negedge i_Reset_n)

if(~i_Reset_n)begin

counter[1:0]<=0;

en1<=0;

end

else begin

en1<=0;

case ({counter[1:0]})

2'b00:counter[1:0]<=2'b01;

2'b01:counter[1:0]<=2'b10;

2'b10:begin counter[1:0]<=2'b11;en1<=1; end

2'b11:counter[1:0]<=2'b00;

default:counter[1:0]<=2'b00;

endcase

end

always @(posedge i_Clock or negedge i_Reset_n)

if(~i_Reset_n)begin

counter[3:2]<=0;

en2<=0;

end

else begin

en2<=0;

case ({en1,counter[3:2]})

3'b100:counter[3:2]<=2'b01;

3'b101:counter[3:2]<=2'b10;

3'b110:begin counter[3:2]<=2'b11;en2<=1; end

3'b111:counter[3:2]<=2'b00;

default:counter[3:2]<=counter[3:2];

endcase

end

always @(posedge i_Clock or negedge i_Reset_n)

if(~i_Reset_n)begin

counter[5:4]<=0;

en3<=0;

end

else begin

en3<=0;

case ({en2,counter[5:4]})

3'b100:counter[5:4]<=2'b01;

3'b101:counter[5:4]<=2'b10;

3'b110:begin counter[5:4]<=2'b11;en3<=1; end

3'b111:counter[5:4]<=2'b00;

default:counter[5:4]<=counter[5:4];

endcase

end

always @(posedge i_Clock or negedge i_Reset_n)

if(~i_Reset_n)

counter[7:6]<=0;

else begin

case ({en3,counter[7:6]})

3'b100:counter[7:6]<=2'b01;

3'b101:counter[7:6]<=2'b10;

3'b110:begin counter[7:6]<=2'b11;end

3'b111:counter[7:6]<=2'b00;

default:counter[7:6]<=counter[7:6];

endcase

end

endmodule

erformance Summary

*******************

Worst slack in design: -0.234

Requested Estimated Requested Estimated Clock Clock

Starting Clock Frequency Frequency Period Period Slack Type Group

--------------------------------------------------------------------------------------------------------------------------

chaoqian|i_Clock 754.1 MHz 641.0 MHz 1.326 1.560 -0.234 inferred Autoconstr_clkgroup_0

==========================================================================================================================

Clock Relationships

*******************

Clocks | rise to rise | fall to fall | rise to fall | fall to rise

---------------------------------------------------------------------------------------------------------------------------

Starting Ending | constraint slack | constraint slack | constraint slack | constraint slack

---------------------------------------------------------------------------------------------------------------------------

chaoqian|i_Clock chaoqian|i_Clock | 1.326 -0.234 | No paths - | No paths - | No paths -

===========================================================================================================================

Note: 'No paths' indicates there are no paths in the design for that pair of clock edges.

'Diff grp' indicates that paths exist but the starting clock and ending clock are in different clock groups.

Interface Information

*********************

No IO constraint found

====================================

Detailed Report for Clock: chaoqian|i_Clock

====================================

Starting Points with Worst Slack

********************************

Starting Arrival

Instance Reference Type Pin Net Time Slack

Clock

-------------------------------------------------------------------------------------------------------------

en1 chaoqian|i_Clock stratixii_lcell_ff regout en1 0.095 -0.234

en2 chaoqian|i_Clock stratixii_lcell_ff regout en2 0.095 -0.234

en3 chaoqian|i_Clock stratixii_lcell_ff regout en3 0.095 -0.234

counter_1[0] chaoqian|i_Clock stratixii_lcell_ff regout counter_1_c[0] 0.095 0.130

counter_3[0] chaoqian|i_Clock stratixii_lcell_ff regout counter_3_c[0] 0.095 0.130

counter[0] chaoqian|i_Clock stratixii_lcell_ff regout counter_c[0] 0.095 0.208

counter[1] chaoqian|i_Clock stratixii_lcell_ff regout counter_c[1] 0.095 0.208

counter_1[1] chaoqian|i_Clock stratixii_lcell_ff regout counter_1_c[1] 0.095 0.208

counter_2[1] chaoqian|i_Clock stratixii_lcell_ff regout counter_2_c[1] 0.095 0.208

counter_3[1] chaoqian|i_Clock stratixii_lcell_ff regout counter_3_c[1] 0.095 0.208

=============================================================================================================

Ending Points with Worst Slack

******************************

Starting Required

Instance Reference Type Pin Net Time Slack

Clock

-----------------------------------------------------------------------------------------------------------------

counter_1[1] chaoqian|i_Clock stratixii_lcell_ff ena en2 0.482 -0.234

counter_2[1] chaoqian|i_Clock stratixii_lcell_ff ena en3 0.482 -0.234

counter_3[1] chaoqian|i_Clock stratixii_lcell_ff ena en1 0.482 -0.234

en2 chaoqian|i_Clock stratixii_lcell_ff datain en221 1.079 0.130

en3 chaoqian|i_Clock stratixii_lcell_ff datain en321 1.079 0.130

counter[1] chaoqian|i_Clock stratixii_lcell_ff datain N_93_i 1.079 0.208

counter_1[0] chaoqian|i_Clock stratixii_lcell_ff datain counter_1_ns_e[0] 1.079 0.208

counter_1[1] chaoqian|i_Clock stratixii_lcell_ff datain N_100_i 1.079 0.208

counter_2[0] chaoqian|i_Clock stratixii_lcell_ff datain counter_2_ns_e[0] 1.079 0.208

counter_2[1] chaoqian|i_Clock stratixii_lcell_ff datain N_107_i 1.079 0.208

=================================================================================================================

module chaoqian(

i_Clock,

i_Reset_n,

cnt

);

input i_Clock;

input i_Reset_n;

output [7:0]cnt;

reg [7:0]counter;

reg en1;

reg en2;

reg en3;

assign cnt=counter;

always @(posedge i_Clock or negedge i_Reset_n)

if(~i_Reset_n)begin

counter[1:0]<=0;

en1<=0;

end

else begin

en1<=0;

case ({counter[1:0]})

2'b00:counter[1:0]<=2'b01;

2'b01:counter[1:0]<=2'b10;

2'b10:begin counter[1:0]<=2'b11;en1<=1; end

2'b11:counter[1:0]<=2'b00;

default:counter[1:0]<=2'b00;

endcase

end

always @(posedge i_Clock or negedge i_Reset_n)

if(~i_Reset_n)begin

counter[3:2]<=0;

en2<=0;

end

else begin

en2<=0;

case ({en1,counter[3:2]})

3'b100:counter[3:2]<=2'b01;

3'b101:counter[3:2]<=2'b10;

3'b110:begin counter[3:2]<=2'b11;en2<=1; end

3'b111:counter[3:2]<=2'b00;

default:counter[3:2]<=counter[3:2];

endcase

end

always @(posedge i_Clock or negedge i_Reset_n)

if(~i_Reset_n)begin

counter[5:4]<=0;

en3<=0;

end

else begin

en3<=0;

case ({en2,counter[5:4]})

3'b100:counter[5:4]<=2'b01;

3'b101:counter[5:4]<=2'b10;

3'b110:begin counter[5:4]<=2'b11;en3<=1; end

3'b111:counter[5:4]<=2'b00;

default:counter[5:4]<=counter[5:4];

endcase

end

always @(posedge i_Clock or negedge i_Reset_n)

if(~i_Reset_n)

counter[7:6]<=0;

else begin

case ({en3,counter[7:6]})

3'b100:counter[7:6]<=2'b01;

3'b101:counter[7:6]<=2'b10;

3'b110:begin counter[7:6]<=2'b11;end

3'b111:counter[7:6]<=2'b00;

default:counter[7:6]<=counter[7:6];

endcase

end

endmodule

erformance Summary

*******************

Worst slack in design: -0.234

Requested Estimated Requested Estimated Clock Clock

Starting Clock Frequency Frequency Period Period Slack Type Group

--------------------------------------------------------------------------------------------------------------------------

chaoqian|i_Clock 754.1 MHz 641.0 MHz 1.326 1.560 -0.234 inferred Autoconstr_clkgroup_0

==========================================================================================================================

Clock Relationships

*******************

Clocks | rise to rise | fall to fall | rise to fall | fall to rise

---------------------------------------------------------------------------------------------------------------------------

Starting Ending | constraint slack | constraint slack | constraint slack | constraint slack

---------------------------------------------------------------------------------------------------------------------------

chaoqian|i_Clock chaoqian|i_Clock | 1.326 -0.234 | No paths - | No paths - | No paths -

===========================================================================================================================

Note: 'No paths' indicates there are no paths in the design for that pair of clock edges.

'Diff grp' indicates that paths exist but the starting clock and ending clock are in different clock groups.

Interface Information

*********************

No IO constraint found

====================================

Detailed Report for Clock: chaoqian|i_Clock

====================================

Starting Points with Worst Slack

********************************

Starting Arrival

Instance Reference Type Pin Net Time Slack

Clock

-------------------------------------------------------------------------------------------------------------

en1 chaoqian|i_Clock stratixii_lcell_ff regout en1 0.095 -0.234

en2 chaoqian|i_Clock stratixii_lcell_ff regout en2 0.095 -0.234

en3 chaoqian|i_Clock stratixii_lcell_ff regout en3 0.095 -0.234

counter_1[0] chaoqian|i_Clock stratixii_lcell_ff regout counter_1_c[0] 0.095 0.130

counter_3[0] chaoqian|i_Clock stratixii_lcell_ff regout counter_3_c[0] 0.095 0.130

counter[0] chaoqian|i_Clock stratixii_lcell_ff regout counter_c[0] 0.095 0.208

counter[1] chaoqian|i_Clock stratixii_lcell_ff regout counter_c[1] 0.095 0.208

counter_1[1] chaoqian|i_Clock stratixii_lcell_ff regout counter_1_c[1] 0.095 0.208

counter_2[1] chaoqian|i_Clock stratixii_lcell_ff regout counter_2_c[1] 0.095 0.208

counter_3[1] chaoqian|i_Clock stratixii_lcell_ff regout counter_3_c[1] 0.095 0.208

=============================================================================================================

Ending Points with Worst Slack

******************************

Starting Required

Instance Reference Type Pin Net Time Slack

Clock

-----------------------------------------------------------------------------------------------------------------

counter_1[1] chaoqian|i_Clock stratixii_lcell_ff ena en2 0.482 -0.234

counter_2[1] chaoqian|i_Clock stratixii_lcell_ff ena en3 0.482 -0.234

counter_3[1] chaoqian|i_Clock stratixii_lcell_ff ena en1 0.482 -0.234

en2 chaoqian|i_Clock stratixii_lcell_ff datain en221 1.079 0.130

en3 chaoqian|i_Clock stratixii_lcell_ff datain en321 1.079 0.130

counter[1] chaoqian|i_Clock stratixii_lcell_ff datain N_93_i 1.079 0.208

counter_1[0] chaoqian|i_Clock stratixii_lcell_ff datain counter_1_ns_e[0] 1.079 0.208

counter_1[1] chaoqian|i_Clock stratixii_lcell_ff datain N_100_i 1.079 0.208

counter_2[0] chaoqian|i_Clock stratixii_lcell_ff datain counter_2_ns_e[0] 1.079 0.208

counter_2[1] chaoqian|i_Clock stratixii_lcell_ff datain N_107_i 1.079 0.208

=================================================================================================================

不明白这个计数器是干什么用的