為何視同一條timing path

时间:10-02

整理:3721RD

点击:

Dear sir,

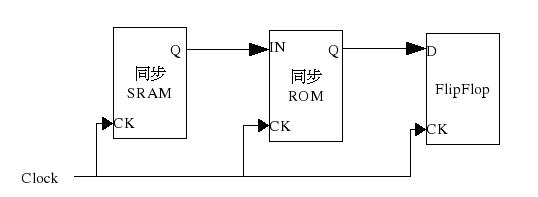

請看圖,所有的記憶體都是同步的,所以我基本上認為因該有兩條timing path,

第一條 : clock -> 同步SRAM -> 同步ROM的data input

第二條 : clock -> 同步ROM -> FlipFlop的data input

但在FPGA與CMOS下做STA時都是只有一條PATH:從clock直接到FlipFlop的data input,途中把同步ROM當成組合邏輯元件似的,將他的delay值加到這調路徑,好奇怪喔,都是同步零件阿。

想要將ROM設成false_path要不好設,請問該如何做?

謝謝。

請看圖,所有的記憶體都是同步的,所以我基本上認為因該有兩條timing path,

第一條 : clock -> 同步SRAM -> 同步ROM的data input

第二條 : clock -> 同步ROM -> FlipFlop的data input

但在FPGA與CMOS下做STA時都是只有一條PATH:從clock直接到FlipFlop的data input,途中把同步ROM當成組合邏輯元件似的,將他的delay值加到這調路徑,好奇怪喔,都是同步零件阿。

想要將ROM設成false_path要不好設,請問該如何做?

謝謝。

有些情况下。在做DFT test的时候ROM、RAM会有In-Out的direct-path,你设置成false-path就可以了。

这没啥好奇怪的,如果该DFF为输入端的第一个DFF,则这些同步器件会被当作逻辑电路来处理,timing path 回从clock 到DFF的D端。

如果两个DFF夹着这些器件那么可能会被当作时序电路来处理。

这时候需要用set_false_path去屏蔽ROM的时序通路。

可是我沒有做DFT阿