同步异步控制信号 仿真出现问题 大家帮忙看看

时间:10-02

整理:3721RD

点击:

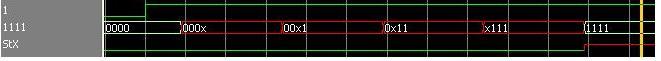

用4个寄存器同步一控制信号,在仿真时还是出现问题,大家帮忙看看, 下边是代码,还有波形。多谢。

input clk;

input start;

output start_real;

reg [3:0] start_shift;

always@(posedge clk)

begin

start_shift <= { start_shift[2:0], start };

if (start_shift == 4'b1111)

start_real <= 1'b1;

else

start_real <= 1'b0;

end

input clk;

input start;

output start_real;

reg [3:0] start_shift;

always@(posedge clk)

begin

start_shift <= { start_shift[2:0], start };

if (start_shift == 4'b1111)

start_real <= 1'b1;

else

start_real <= 1'b0;

end

start_shift没有初始状态。

一般在电路上不会有错误,建议 START_REAL = SH[3:1];

没有复位信号,输出需要定义为reg类型

没有复位信号,输出需要定义为reg类型