SDRAM控制问题请教:为何用的器件模型读数据的时候是高阻Z

遇到下面的问题了

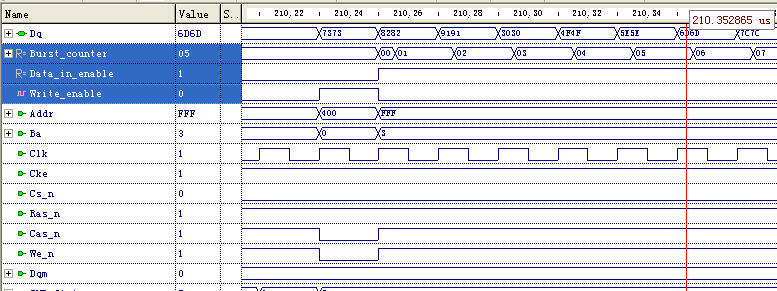

为何在写的过程 列地址的第一位在最后给写成zzzz了?

见下面的记录

列地址最大255

.....

SDRAM_TEST_tb.mt48lc4m16a2 : at time 215250.0 ns WRITE: Bank = 0 Row = 0, Col = 250, Data = 5959

SDRAM_TEST_tb.mt48lc4m16a2 : at time 215270.0 ns WRITE: Bank = 0 Row = 0, Col = 251, Data = 6868

SDRAM_TEST_tb.mt48lc4m16a2 : at time 215290.0 ns WRITE: Bank = 0 Row = 0, Col = 252, Data = 7777

SDRAM_TEST_tb.mt48lc4m16a2 : at time 215310.0 ns WRITE: Bank = 0 Row = 0, Col = 253, Data = 8686

SDRAM_TEST_tb.mt48lc4m16a2 : at time 215330.0 ns WRITE: Bank = 0 Row = 0, Col = 254, Data = 9595

SDRAM_TEST_tb.mt48lc4m16a2 : at time 215350.0 ns WRITE: Bank = 0 Row = 0, Col = 255, Data = 3434

SDRAM_TEST_tb.mt48lc4m16a2 : at time 215370.0 ns WRITE: Bank = 0 Row = 0, Col = 0, Data = zzzz

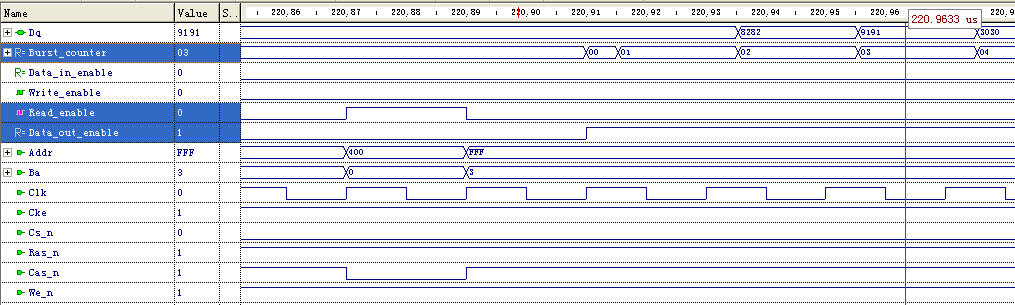

SDRAM_TEST_tb.mt48lc4m16a2 : at time 220915.0 ns READ : Bank = 0 Row = 0, Col = 0, Data = zzzz

SDRAM_TEST_tb.mt48lc4m16a2 : at time 220935.0 ns READ : Bank = 0 Row = 0, Col = 1, Data = 8282

SDRAM_TEST_tb.mt48lc4m16a2 : at time 220955.0 ns READ : Bank = 0 Row = 0, Col = 2, Data = 9191

SDRAM_TEST_tb.mt48lc4m16a2 : at time 220975.0 ns READ : Bank = 0 Row = 0, Col = 3, Data = 3030

SDRAM_TEST_tb.mt48lc4m16a2 : at time 220995.0 ns READ : Bank = 0 Row = 0, Col = 4, Data = 4f4f

SDRAM_TEST_tb.mt48lc4m16a2 : at time 221015.0 ns READ : Bank = 0 Row = 0, Col = 5, Data = 5e5e

SDRAM_TEST_tb.mt48lc4m16a2 : at time 221035.0 ns READ : Bank = 0 Row = 0, Col = 6, Data = 6d6d

发现在仿真出来的波形在写与读的开始位置出有点不对劲

见附图

那位用过类似器件模型仿真的说说可能的缘故

仔细看看器件模型Spec,上面应该会有使用说明的