仿真结果有问题,请教大家是什么原因。

时间:10-02

整理:3721RD

点击:

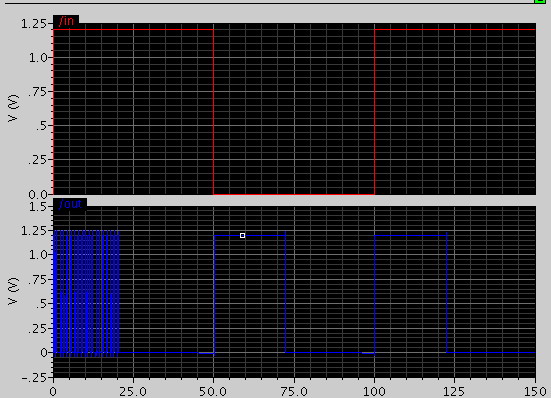

由于想测一下反相器的延时,就在in后面串连了1000个反相器,out输出是输入信号与延时之后信号的异或运算。那么输出的高电平就是延时了。

不知道为什么开始的波形不稳定? 我加的激励如下,IN的上升延时20ps ;vdd开始是0,50ps时才逐渐上升到1.2v。

_vin (in 0) vsource dc=0 val0=0 val1=1.2 delay=0 rise=20p fall=20p width=50n period=100n type=pulse

_vvdd! (vdd! 0) vsource wave=[ 0 0 50p 1.2 ] type=pwl

_vvss! (vss! 0) vsource dc=0 type=dc

不是数字仿真吧,好险是模拟啊?

有点儿像Ring Osc,刚开始会不稳定的。稳定时间和你的串接delay有关系的