新手提问,实现电子秒表的存读取功能

时间:10-02

整理:3721RD

点击:

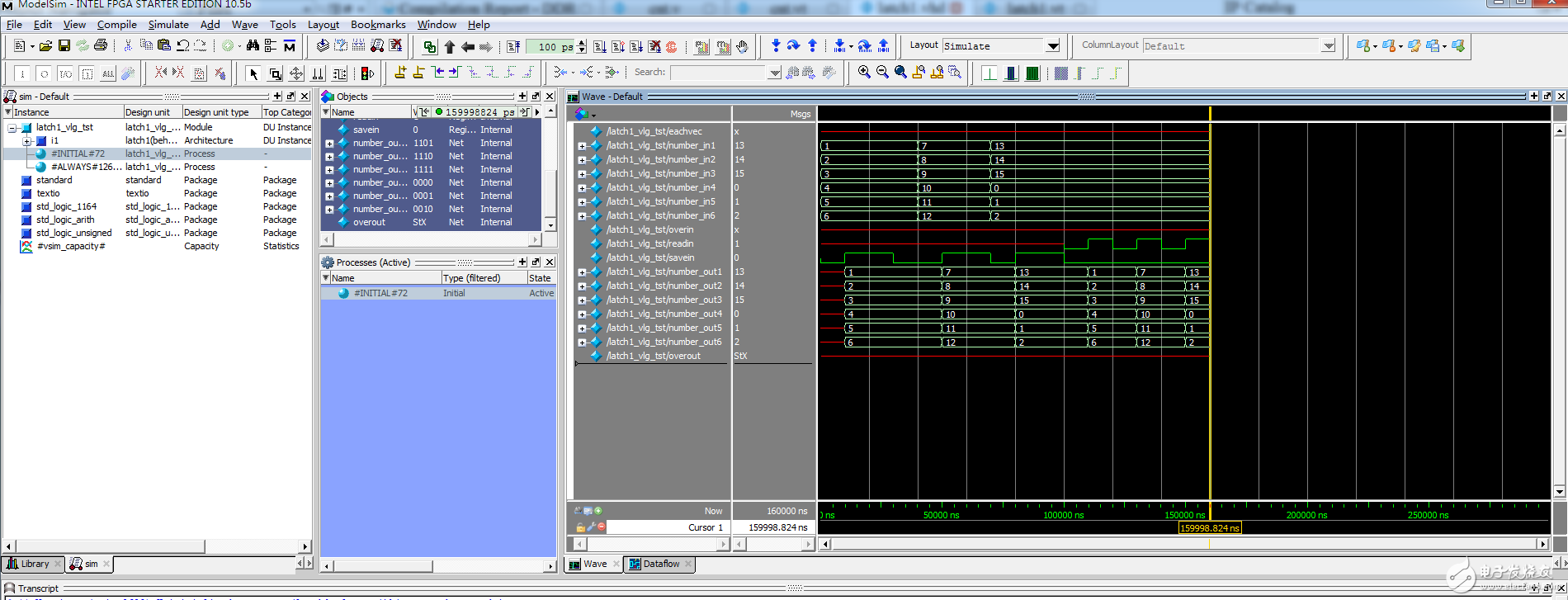

用fpga做一个秒表 能实现存读取数据的功能,要求保存三组数据

这是我的存储器的模块,硬件运行时无法实现以上功能,请问哪里出错了?非常感谢

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_arith.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity latch is

Port ( savein : in STD_LOGIC;

readin : in STD_LOGIC;

overin : in STD_LOGIC;

number_in1 : in STD_LOGIC_VECTOR (3 downto 0);

number_in2 : in STD_LOGIC_VECTOR (3 downto 0);

number_in3 : in STD_LOGIC_VECTOR (3 downto 0);

number_in4 : in STD_LOGIC_VECTOR (3 downto 0);

number_in5 : in STD_LOGIC_VECTOR (3 downto 0);

number_in6 : in STD_LOGIC_VECTOR (3 downto 0);

overout : out STD_LOGIC;

number_out1 : out STD_LOGIC_VECTOR (3 downto 0);

number_out2 : out STD_LOGIC_VECTOR (3 downto 0);

number_out3 : out STD_LOGIC_VECTOR (3 downto 0);

number_out4 : out STD_LOGIC_VECTOR (3 downto 0);

number_out5 : out STD_LOGIC_VECTOR (3 downto 0);

number_out6 : out STD_LOGIC_VECTOR (3 downto 0));

end latch;

architecture Behavioral of latch is

signal cnt : STD_LOGIC_VECTOR (2 downto 0);

signal num : STD_LOGIC_VECTOR (2 downto 0);

signal number01,number02,number03,number04,number05,number06 : STD_LOGIC_VECTOR (3 downto 0);

signal number11,number12,number13,number14,number15,number16 : STD_LOGIC_VECTOR (3 downto 0);

signal number21,number22,number23,number24,number25,number26 : STD_LOGIC_VECTOR (3 downto 0);

begin

process(savein)

begin

if rising_edge(savein) then

if cnt number01 number11 number21 number_out1 number_out1 number_out1 number_out1 number_out1<=number_in1;

number_out2<=number_in2;

number_out3<=number_in3;

number_out4<=number_in4;

number_out5<=number_in5;

number_out6<=number_in6;

end case;

end process;

end Behavioral;

这是我的存储器的模块,硬件运行时无法实现以上功能,请问哪里出错了?非常感谢

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_arith.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity latch is

Port ( savein : in STD_LOGIC;

readin : in STD_LOGIC;

overin : in STD_LOGIC;

number_in1 : in STD_LOGIC_VECTOR (3 downto 0);

number_in2 : in STD_LOGIC_VECTOR (3 downto 0);

number_in3 : in STD_LOGIC_VECTOR (3 downto 0);

number_in4 : in STD_LOGIC_VECTOR (3 downto 0);

number_in5 : in STD_LOGIC_VECTOR (3 downto 0);

number_in6 : in STD_LOGIC_VECTOR (3 downto 0);

overout : out STD_LOGIC;

number_out1 : out STD_LOGIC_VECTOR (3 downto 0);

number_out2 : out STD_LOGIC_VECTOR (3 downto 0);

number_out3 : out STD_LOGIC_VECTOR (3 downto 0);

number_out4 : out STD_LOGIC_VECTOR (3 downto 0);

number_out5 : out STD_LOGIC_VECTOR (3 downto 0);

number_out6 : out STD_LOGIC_VECTOR (3 downto 0));

end latch;

architecture Behavioral of latch is

signal cnt : STD_LOGIC_VECTOR (2 downto 0);

signal num : STD_LOGIC_VECTOR (2 downto 0);

signal number01,number02,number03,number04,number05,number06 : STD_LOGIC_VECTOR (3 downto 0);

signal number11,number12,number13,number14,number15,number16 : STD_LOGIC_VECTOR (3 downto 0);

signal number21,number22,number23,number24,number25,number26 : STD_LOGIC_VECTOR (3 downto 0);

begin

process(savein)

begin

if rising_edge(savein) then

if cnt number01 number11 number21 number_out1 number_out1 number_out1 number_out1 number_out1<=number_in1;

number_out2<=number_in2;

number_out3<=number_in3;

number_out4<=number_in4;

number_out5<=number_in5;

number_out6<=number_in6;

end case;

end process;

end Behavioral;

貌似可以的,建议使用片上RAM

程序是可以的啊,看看是不是其他地方的问题啊,