关于DDR2 ip核用户接口的一些问题讨论

时间:10-02

整理:3721RD

点击:

最近在学习DDR2 ip核 现在初步实现了 数据的读写,欢迎做过和正在学习的伙伴们进来探讨探讨。 最近在看《例说fpga》这本书时,遇到一个问题 是关于 用户接口 local_burstbegin的

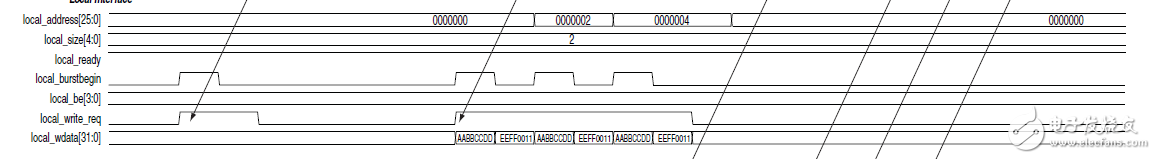

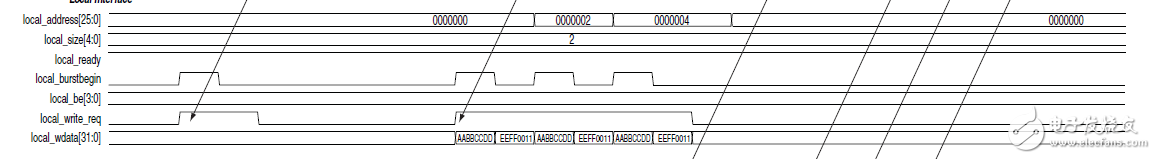

altera的官方手册上定义 local_burstbegin必须在读写请求时拉高,并且要求在写突发的第一个周期后拉低。时序图如下:

在读突发时 是跟随读请求一起的

但是在《例说FPGA》书中 是这样连接local_burstbegin的

将local_burstbegin 与 (local_read_req| local_write_req)相连接

这样local_burstbegin 会在写突发时时序上与 存在冲突

但是这个程序经验证也是正确的 可以将数据读写

所以说local_burstbegin 的时序要求也不是那么严格吗?

altera的官方手册上定义 local_burstbegin必须在读写请求时拉高,并且要求在写突发的第一个周期后拉低。时序图如下:

在读突发时 是跟随读请求一起的

但是在《例说FPGA》书中 是这样连接local_burstbegin的

将local_burstbegin 与 (local_read_req| local_write_req)相连接

这样local_burstbegin 会在写突发时时序上与 存在冲突

但是这个程序经验证也是正确的 可以将数据读写

所以说local_burstbegin 的时序要求也不是那么严格吗?

帮顶 哈哈 好高深的样子

不会冲突吧,只有在有读写请求时才会local_burstbegin置高,而且这两种信号持续时间很短,一般只有数据传输时才有效。local_read_req| local_write_req作为端口信号输入没问题吧

手册中给出的时序图上,local_burstbegin是只在突发操作的第一个周期拉高,过了第一个周期就要拉低的 。

手册中给出的时序图上,local_burstbegin是只在突发操作的第一个周期拉高,过了第一个周期就要拉低的 。

手册中给出的时序图上,local_burstbegin是只在突发操作的第一个周期拉高,过了第一个周期就要拉低的 。