做过DDR ip核 的进来讨论讨论

时间:10-02

整理:3721RD

点击:

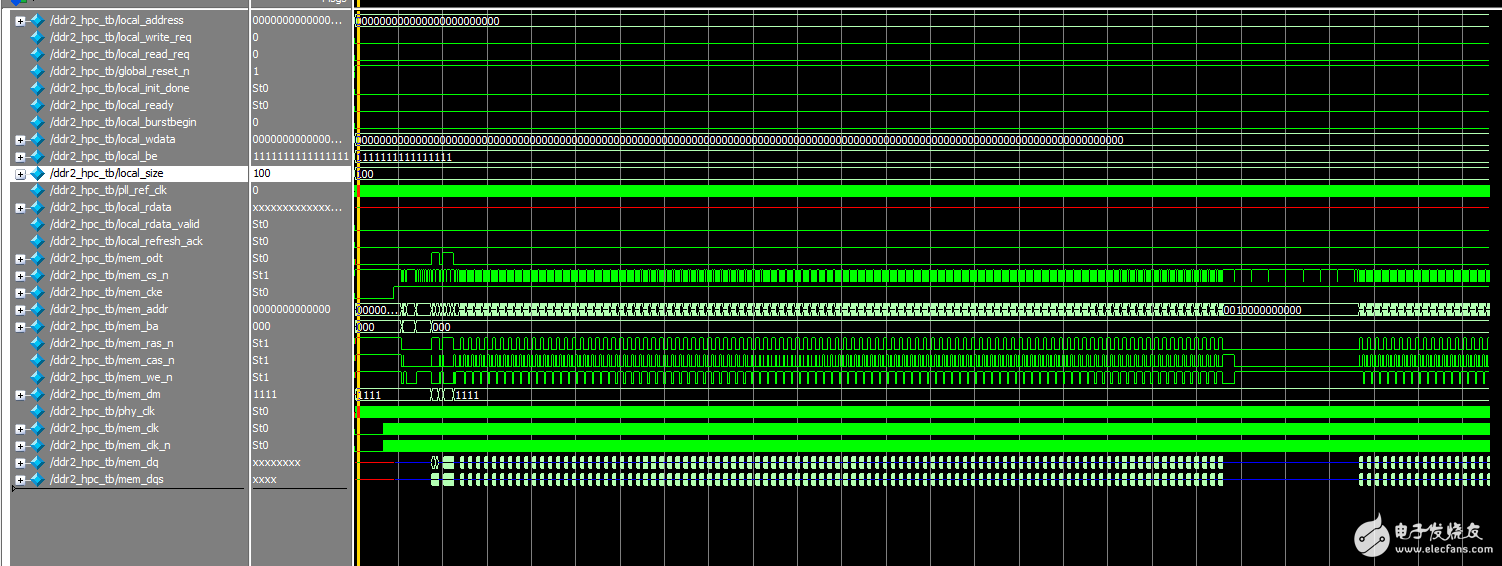

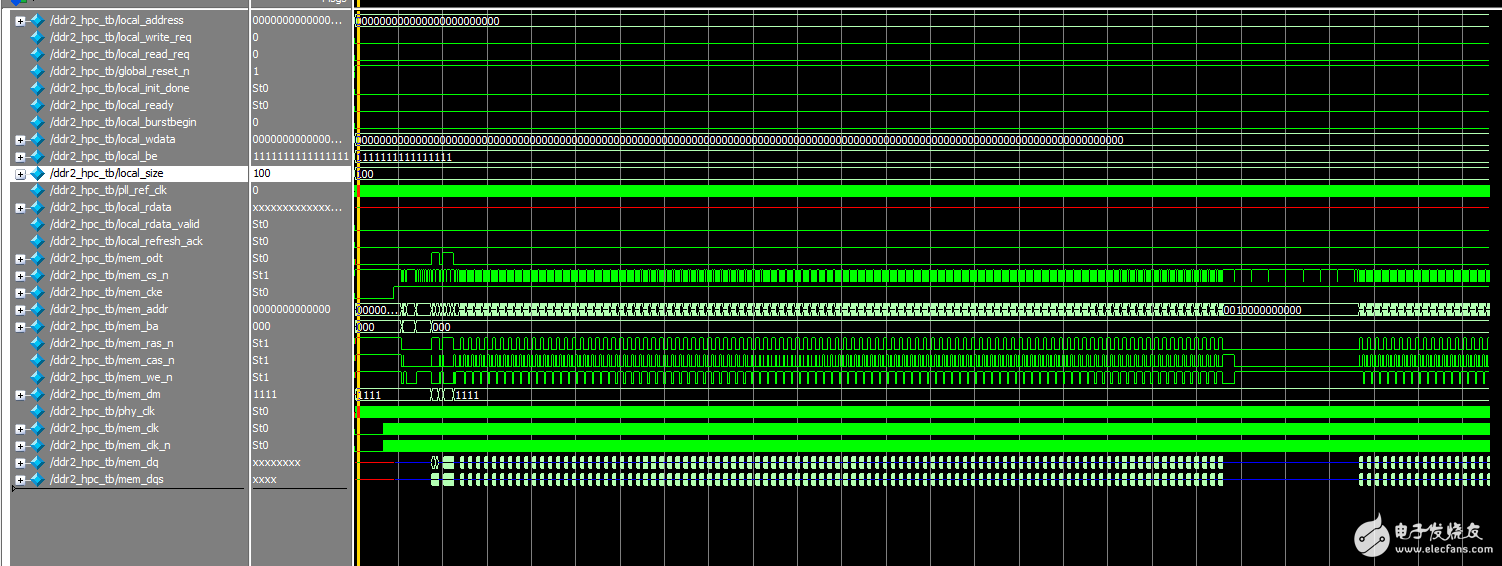

调用了DDR2控制器完整的ip核, 加了一个 黑金给的仿真模型(因为板子上的DDR2 就是这个), 仿真的时候一直收不到local_init_done 拉高的信号,所以后面给的命令也没有实现,但是mem_dq线上却有数据出现(00000000或ffffffff), 之前用别的仿真模型是可以的 ,下面是仿真结果图。

下面是tb仿真的部分

/ 初始化

initial begin

pll_ref_clk = 1 ;

global_reset_n = 0 ;

local_write_req = 0 ;

local_read_req = 0 ;

local_burstbegin = 0 ;

local_address = 0 ;

local_be =16'hffff ;

local_size = 4 ;

local_wdata = 0 ;

#200

global_reset_n = 1 ;

@(posedge phy_clk )

@(posedge phy_clk )

@ (posedge local_init_done) //等待上电结束

#200

@(posedge phy_clk)

//发送一次写突发

local_write_req = 1 ;

local_address = 24'h001000 ;

local_burstbegin = 1 ;

local_wdata = 128'h33221100;

@(posedge phy_clk)

local_burstbegin = 0 ;

local_wdata = 128'h77665544;

@(posedge phy_clk)

local_wdata = 128'hbbaa9988 ;

@(posedge phy_clk)

local_wdata = 128'hffeeddcc ;

@(posedge phy_clk)

local_write_req = 0 ;

#200

@(posedge phy_clk) //发送一次读请求

local_read_req = 1 ;

local_address = 24'h001000 ;

local_burstbegin = 1 ;

@(posedge phy_clk)

local_burstbegin = 0 ;

local_read_req = 0 ;

@(posedge phy_clk)

@(posedge local_ready ) // 读突发结束

#200 $stop ;

end

always #10 pll_ref_clk = ~pll_ref_clk ;

endmodule

下面是tb仿真的部分

/ 初始化

initial begin

pll_ref_clk = 1 ;

global_reset_n = 0 ;

local_write_req = 0 ;

local_read_req = 0 ;

local_burstbegin = 0 ;

local_address = 0 ;

local_be =16'hffff ;

local_size = 4 ;

local_wdata = 0 ;

#200

global_reset_n = 1 ;

@(posedge phy_clk )

@(posedge phy_clk )

@ (posedge local_init_done) //等待上电结束

#200

@(posedge phy_clk)

//发送一次写突发

local_write_req = 1 ;

local_address = 24'h001000 ;

local_burstbegin = 1 ;

local_wdata = 128'h33221100;

@(posedge phy_clk)

local_burstbegin = 0 ;

local_wdata = 128'h77665544;

@(posedge phy_clk)

local_wdata = 128'hbbaa9988 ;

@(posedge phy_clk)

local_wdata = 128'hffeeddcc ;

@(posedge phy_clk)

local_write_req = 0 ;

#200

@(posedge phy_clk) //发送一次读请求

local_read_req = 1 ;

local_address = 24'h001000 ;

local_burstbegin = 1 ;

@(posedge phy_clk)

local_burstbegin = 0 ;

local_read_req = 0 ;

@(posedge phy_clk)

@(posedge local_ready ) // 读突发结束

#200 $stop ;

end

always #10 pll_ref_clk = ~pll_ref_clk ;

endmodule

你这个IP核哪来的啊

围观一下吧 毕竟不会

仿真时候,需要跳过校准。DDR2在仿真时候默认是有快速校准模式的,据说这个模式得跑几分钟才能跑完,然后才会正常工作。为了节约时间,跳过校准这个步骤吧,具体怎么跳过,可以百度啦,不会的话再来问我,也可以去群里找我。

解决了 谢谢小梅哥