凔海笔记之FPGA(三):聊聊FPGA的内部结构_下

时间:10-02

整理:3721RD

点击:

FPGA就好像一个平台,用简单的器件和复杂的逻辑构建起来的。这个平台大概由六部分组成,分别为基本可编程逻辑模块(CLB)、可编程输入/输出模块(IOB)、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。对于不同型号的芯片,其内部结构也会有些变化,但原理都也差不多,所以咱不必在意说的是何种芯片,下面就以鄙陋只见说芯片之精妙。

1、可编程逻辑模块

逻辑块(Logic Block),Altera称之为逻辑阵列块(LAB),Xilinx称之为可配置逻辑课(CLB),我更喜欢CLB这个称呼,因为它说得够清楚,虽然我用的是Altera公司的芯片吧(*^__^*) 。我们所说的Verilog编程,可以说就是对CLB的配置,它可以实现绝大多数的逻辑功能。

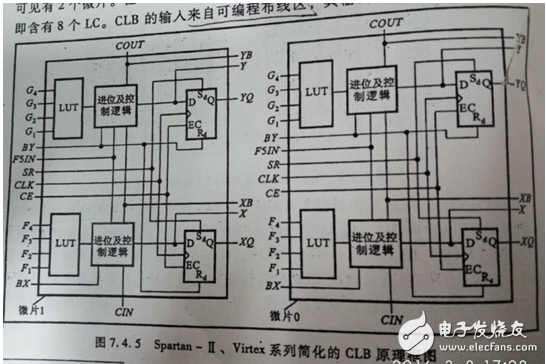

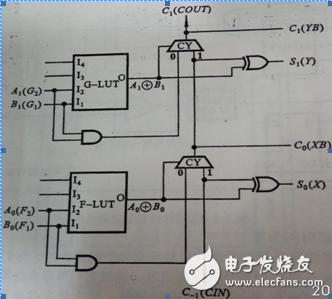

这是从书上拍下了的,这是CLB基础的逻辑单元(LC)Logic Cell,一个CLB包含4个LC。每个LC中包括4输入LUT、进位及控制逻辑和D触发器各一个。而每2个LC放在一个微片上,上图就是俩个微片。微片就是很小很小的一个模块,或可理解为像人体细胞一样吧。

其中LUT(Look-Up Table)即查找表,它的本质是一个16X1的SRAM,SRAM是英文Static RAM的缩写,即静态随机存储器。我们可以认为SRAM是这个东西

现在我想每个格子都放一样东西,并方便寻找给每个格子编号,则格子的编号就可以看做格子的地址,如果每个格子只能放一个苹果或是橘子,那么上图就可以理解为一个20X1的RAM,当然,这只是一种比喻。

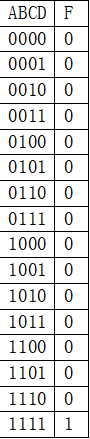

我们通过Verilog语言可以写出逻辑电路,例如F=A&B&C&D,FPGA开发软件会自动计算逻辑电路的所有可能,并把结果放入SRAM,这一过程就是所谓的编程。就那F=A&B&C&D来说,ABCD的组合共有十六组,如下表

当我们下载的时候,软件会自动把上述表格的值送给SRAM,我们ABCD取不同值时,LUT就根据地址进行找到数输出。也就是说,FPGA并不知道我们进行了F=A&B&C&D这一计算,它只是根据我们的输入进行寻址。把LUT与数据选择器配合使用,就可以实现组合逻辑功能,当与触发器结合就可以实现时序逻辑电路的基本功能。

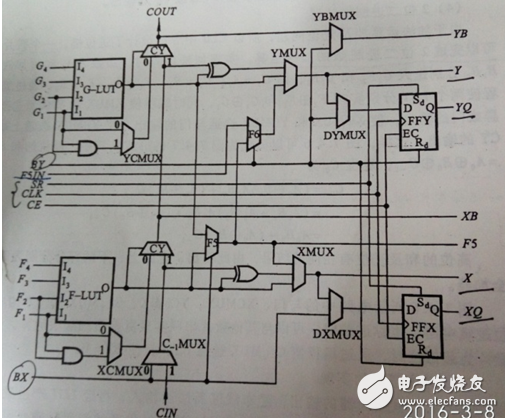

这是一个微片的原理图。看着好复杂哈,想晕,但还是坚持一点点认识吧。

图中除了数据选择器F5、CY、F6外都是可编程的。微片有15个输入端和8个输出端。

15个输入端包括俩组LUT、SR触发器控制端,CLK时钟信号输入端,CE时钟使能控制端。F5IN级联输入端,BX、BY旁路输入端、CIN进位链输入端

8个输出包括2个组合逻辑输出端X和Y,2个寄存器输出端XQ和YQ,2个算数运算进位端BX和BY,1个级联输出端F5和1个进位链输出端COUT。

在我第一次看这些名词时,真是怀疑自己的智商了。

LUT不废话,过

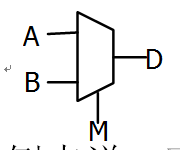

数据选择器:

由M来控制AB哪个与D搭上线,就是M来选择AB输出哪一个,例如当M=0时A的值输出,当M=1时B的值输出,

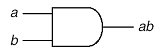

与门:

ab同为一输出1.否则为0.

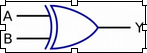

异或:

AB不同时输出1.

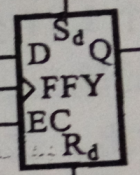

触发器:

实现时序逻辑就是因为这个,D数据输入,FFY时钟信号输入,它来一拍,数据传输一个。EC时钟使能,Sd触发器控制,Rd复位控制。

下面就通过举例来说一下各种功能

(1)实现4变量的任意逻辑函数。

例如要实现F=A^B&C||D。那么就如上表格方式计算出所有的可能,将ABCD依次送给F1~F4,O端得到4变量逻辑函数的结果。该结果可以经过XMUX直接从X输出,也可以经DCMUX和D触发器由XQ输出。

(2)实现5变量的任意逻辑函数

5变量?!那一个LUT肯定是不够了。F=A^B&C||D&E肿么办?这时BX成了救世主,我们把ABCD这四个数据时同时送到送入F1~F4以及G1~G4的同时,将第五个数E送给BX。Why?Σ( ° △ °|||)︴因为五个数有32种可能,一个LUT只能存储16种,这样俩个就存储32种啦。而且,如果我们在G-LUT中放的是ABCD任意值,而E为1,在F-LUT中放的也是ABCD任意值,但E=0。这时候第五个变量的输入就起到选择这俩个LUT哪个输出!

真的太巧妙了。

(3)实现6变量任意逻辑函数

有了5变量的基础,实现六变量就好理解了,六变量逻辑函数需要俩个微片。因为由2^6=64嘛。我们假设要实现W=A^B&C||D&E&F。则可以让微片一号的G-LUT存放地址ABCD任意值E=0,F=1,F-LUT存放ABCD任意值E=1,F=1。E从BX输入。微片二号G-LUT存放地址ABCD任意值E=0,F=0,F-LUT存放ABCD任意值E=1,F=0。E从BX输入,F从BY输入。微片一号从F5输出值接到微片二号的F5IN即可完成。结果可经过YMUX从Y输出,可再经DYBMUX由触发器输出。

(4)2位二进制加法器

一个微片可以实现2位二进制的加法运算就是11+11=110,10+01=11这些,加法器是非常重要的器件,日后详谈。在FPGA内部中,实现加法时,加数A0A1和被加数B0B1分别送入G2F2和G1F1,即G2=A1,G1=B1,F2=A0,F1=B0。实现F2⊕F1和G2⊕G1,由于加法涉及到了进位问题,故CLB专门设计了一个叫做进位链的东西以便实现进位操作。同时,通过编程使XMUX和YMUX选通异或门的输出。电路上下俩个是全加器。图中,与门、XCMUX、YCMUX、C-1MUX和CY构成进位逻辑电路。也称进位链,可以与其他微片串联实现更多的加法运算。当此微片为最低位时,通过编程使C-1MUX选通BX,且使BX=0。

就这个微片,小小的微片,愣生生的“山寨”了小俩千字,真佩服设计者的智慧,如果将此看做一件艺术品的话,我想匠心独运名副其实。

山寨源:

[1]度娘友情提供

[2]康华光老师主编的电子技术基础数字部分(第五版)全程赞助

(未完待续)

欲瞧凔海笔记之单片机、FPGA等系列文章,请戳下面链接(*^__^*) 嘻嘻……

凔海笔记

收藏起来,学习学习

收藏起来,学习学习

小编出现多次LUT打成TLU,

支持小编

谢谢指正,已改

感谢小编分享

感觉后面的加法器部分和六输入变量查找表部分讲的不是很清楚,

小编好,请问小编笔记里提到的书是哪本?