用Quartus II 13.0 仿真,功能仿真能正常出来,但是到时序仿真就总是报错是什么原因?

时间:10-02

整理:3721RD

点击:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity myfist is

port( clk: in std_logic;

reset: in std_logic;

en: in std_logic;

q: out std_logic_vector(3 downto 0));

end myfist;

architecture behave of myfist is

signal q_n: std_logic_vector(3 downto 0);

begin

process( clk, reset, en, q_n )

begin

if (reset = '1') then

q_n '0');

elsif rising_edge(clk) then

if en = '1' then

q_n <= q_n + 1;

end if;

end if;

end process;

q <= q_n;

end behave;

testbench:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity myfist_tb is

constant ClockPeriod: time := 40 ns;

end myfist_tb;

architecture myfist_tb_arch of myfist_tb is

component myfist is

port (clk: in std_logic;

reset : in std_logic;

en : in std_logic;

q : out std_logic_vector(3 downto 0));

end component;

signal clock , reset , en: std_logic;

signal q: std_logic_vector(3 downto 0);

begin

CounterInstance: myfist port map (clock ,reset, en, q);

simProcess: process

begin

reset <= '1';

wait for 50 ns;

reset <='0';

wait for 1000 ns;

reset <= '0';

end process simprocess;

en <= '0' after 0 ns,

'1' after 50 ns,

'0' after 850 ns,

'1' after 900 ns;

ClockProcess: process (clock, reset )

begin

if (reset ='1') then

clock <= '0';

else

clock <= not clock after ClockPeriod;

end if;

end process ClockProcess;

end myfist_tb_arch;

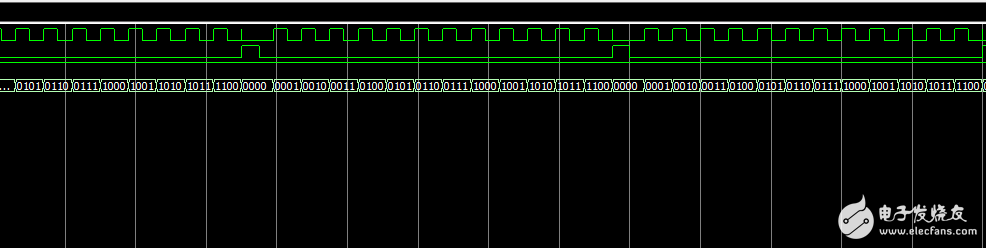

功能仿真:

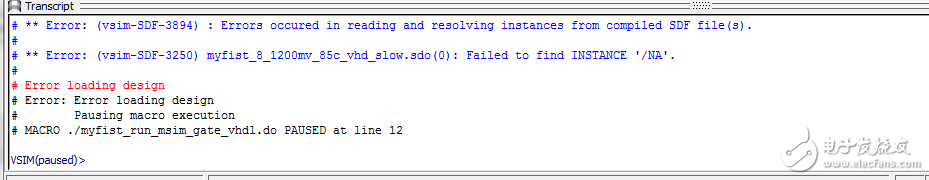

时序仿真:、

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity myfist is

port( clk: in std_logic;

reset: in std_logic;

en: in std_logic;

q: out std_logic_vector(3 downto 0));

end myfist;

architecture behave of myfist is

signal q_n: std_logic_vector(3 downto 0);

begin

process( clk, reset, en, q_n )

begin

if (reset = '1') then

q_n '0');

elsif rising_edge(clk) then

if en = '1' then

q_n <= q_n + 1;

end if;

end if;

end process;

q <= q_n;

end behave;

testbench:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity myfist_tb is

constant ClockPeriod: time := 40 ns;

end myfist_tb;

architecture myfist_tb_arch of myfist_tb is

component myfist is

port (clk: in std_logic;

reset : in std_logic;

en : in std_logic;

q : out std_logic_vector(3 downto 0));

end component;

signal clock , reset , en: std_logic;

signal q: std_logic_vector(3 downto 0);

begin

CounterInstance: myfist port map (clock ,reset, en, q);

simProcess: process

begin

reset <= '1';

wait for 50 ns;

reset <='0';

wait for 1000 ns;

reset <= '0';

end process simprocess;

en <= '0' after 0 ns,

'1' after 50 ns,

'0' after 850 ns,

'1' after 900 ns;

ClockProcess: process (clock, reset )

begin

if (reset ='1') then

clock <= '0';

else

clock <= not clock after ClockPeriod;

end if;

end process ClockProcess;

end myfist_tb_arch;

功能仿真:

时序仿真:、

功能仿真: