CPLD 下降沿触发信号

process(clk, rst )

begin

if rst = '1' then

count <= 0;

pin_out_o <= '1';

elsif rising_edge(clk) then

if pin_in_fall = '1' then

pin_out_o <= '1';

elsif count = 5 then

pin_out_o <= '0';

count <= 0;

elsif pin_out_o = '1' then

count <= count + 1;

end if;

end process;

pin_out <= pin_out_o;

process(clk, rst )

begin

if rst = '1' then

temp1 <= '0';

temp2 <= '0';

elsif rising_edge(clk) then

temp1 <= pin_in;

temp2 <= temp1;

end if;

end process;

pin_in_fall <= not temp1 and temp2;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.std_logic_unsigned.all;

use IEEE.std_logic_arith.all;

entity latch_A is

PORT(

pin_in :IN STD_LOGIC; --输入

clk :IN STD_LOGIC; --输入主频

pin_out :OUT STD_LOGIC --输出管脚

);

end latch_A;

architecture Behavioral of latch_A is

SIGNAL output_reg:STD_LOGIC:='0';

--signal cnt: STD_LOGIC_VECTOR(2 downto 0);

BEGIN

PROCESS

VARIABLE cnt: INTEGER:=0;--to 5;

BEGIN

WAIT UNTIL(RISING_EDGE(clk));

IF pin_in='0' THEN

--IF (pin_in'event AND pin_in='1') THEN --AND cnt=5 THEN --下降沿检测不能用多个状态 只有一个IF

--IF falling_edge(pin_in) THEN

IF cnt=20 THEN

--cnt:=0;

output_reg<='0';

ELSE --IF cnt<"101" THEN

cnt:=cnt+1;

output_reg<='1';

--END IF;

END IF;

ELSE IF pin_in='1' THEN

output_reg<='0';

cnt:=0;

END IF;

END IF;

END PROCESS;

pin_out<=output_reg;

end Behavioral;

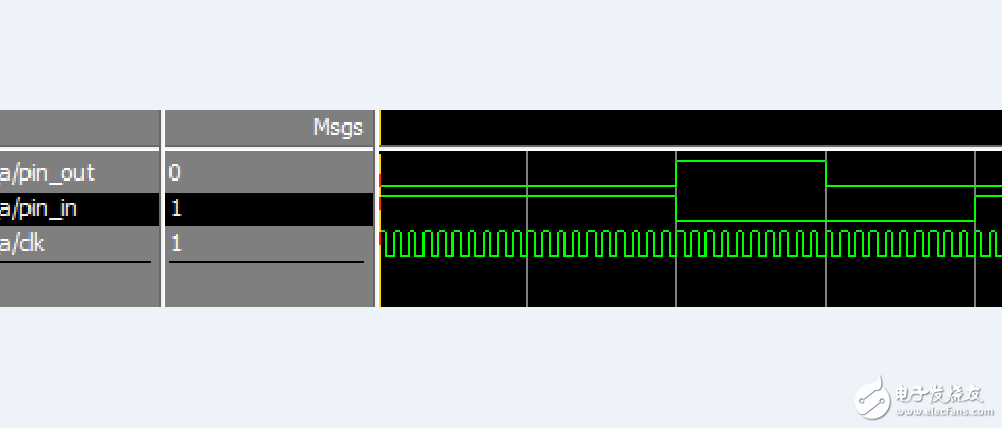

这是自己的代码,但是输出不稳定