QuartusII里面引脚分配该按照什么规律进行

时间:10-02

整理:3721RD

点击:

实在是搞不懂了,每次下到板子上都是出现这种情况,请会做的大哥大姐指点一下,不胜感激!

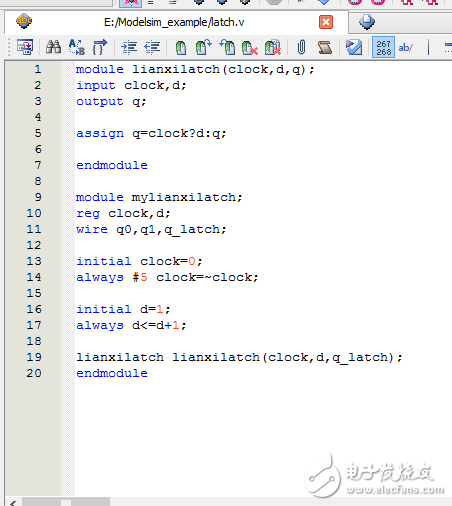

这个是程序这个是引脚分配

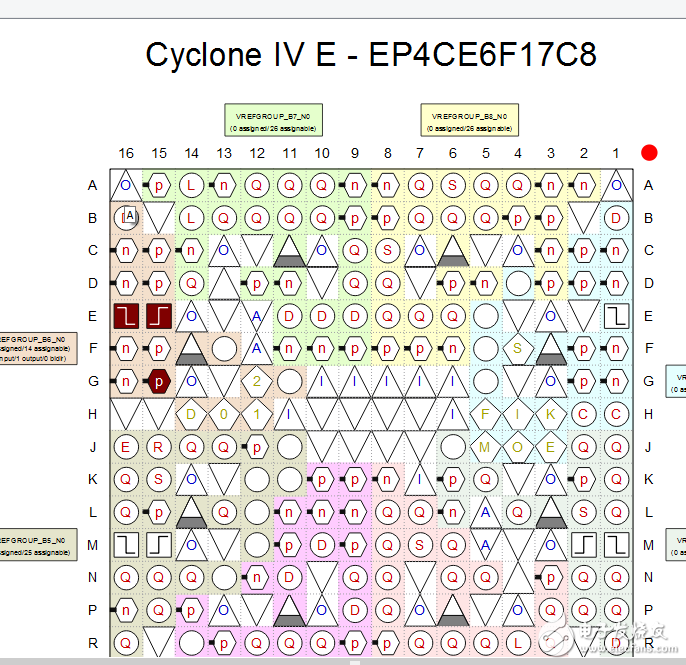

这个是最后板子上显示的结果,没任何反应,我用的是黑金的板子,芯片是EP4CE6F17C8

这个是最后板子上显示的结果,没任何反应,我用的是黑金的板子,芯片是EP4CE6F17C8

这个是程序这个是引脚分配

这个是最后板子上显示的结果,没任何反应,我用的是黑金的板子,芯片是EP4CE6F17C8

这个是最后板子上显示的结果,没任何反应,我用的是黑金的板子,芯片是EP4CE6F17C8不好意思,图被吃了,1是程序的图,2是引脚分配的图

要看板子的设计文档吧。看看哪个管脚连到什么器件。

你的程序编译成功了?

成功了啊,是一个比较简单的程序

是那个用户手册吗?

要注意电源和地的PIN脚,这个不能用作信号脚。否则容易短接。另外特别注意GPIO的状态,不同的driver相互冲突的话,也会影响芯片工作的。

你有没有已经弄好的实例能不能让我参考一下,麻烦了

要看原理图,结合原理图确定引脚连得是什么

是这个板子设计的原理图,或者直接看pcb,把各个管脚的连接关系弄明白。然后在pin assigner里面直接照着来就行了。

你是不是直接拷的光盘里的程序呀,关盘里面不是有教步骤吗?引脚分配直接看脚本文件呀。

我用的就是这个,你可以自动分配的

你想要什么效果啊,你这是什么程序啊,仿真用的吧

哎呦我c,什么时候的帖子了,逗

QuartusII中四选一选择器