xilinx 时序分析及约束

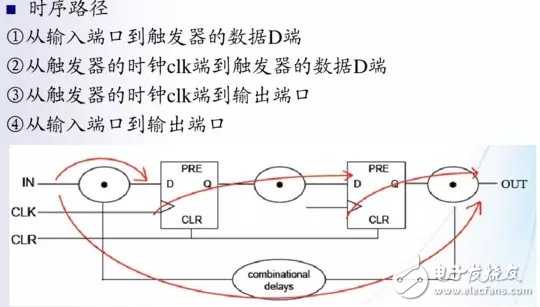

一、基本时序路径

1、clock-to-setup 周期约束

跨时钟域约束:

(1)当源触发器和目标触发器的驱动时钟不同,且时钟的占空比不是50%时,Clock-to-Setup路径被限制为两个时钟高低电平中最短的那一段。

(2)如果源目的触发器使用不同的时钟网络驱动,则要求目标触发器的时钟周期必须大于Clock-to-Setup路径延时,且将其作为允许的最大延时值。

2、clock-to-pad

(1)offset= out "time"[units] after "clkname"[TIMEGRP groupname];//[]为选填

(2)TIMESPEC "TSname" = from "group1" to "group2" value;

//TSname必须以TS开头,group1:起始路径 2:目的路径 value默认ns也可以写MHZ或者表达式

3、pad-to-pad 中间包含所有组合逻辑,但没有同步逻辑

4、 pad-to-setup

(1) offset= in "time" before"clkname";

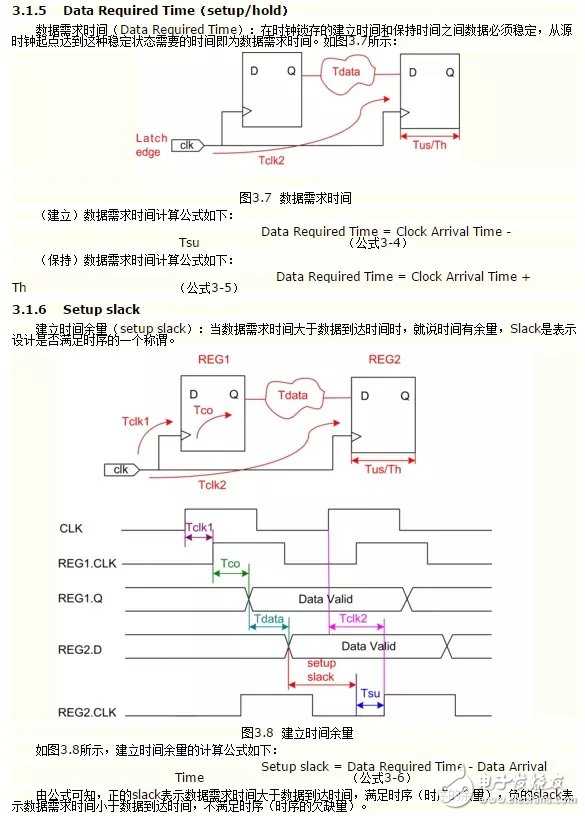

5、时序裕量 slack=约束要求时钟周期 - 实际时钟周期

二、全局时钟和第二全局时钟资源

1.IBUFG/IBUFGDS+ BUFG

2.Logic + BUFG 的使用方法:

当某个信号(时钟、 使能、 快速路径)的扇出非常大, 并且要求抖动延迟最小时, 可以使用 BUFG驱动该信号,使该信号利用全局时钟资源。但需要注意的是,普通 IO 的输入或普通片内信号进入全局时钟布线层需要一个固有的延时,一般在 10ns 左右,即普通IO和普通片内信号从输入到 BUFG 输出有一个约 10ns 左右的固有延时,但是 BUFG的输出到片内所有单元(IOB、CLB、选择性块 RAM)的延时可以忽略不计为“0”ns。

3. IBUFG + DCM + BUFG 的使用方法

4.Logic + DCM + BUFG 的使用方法

5.第二全局时钟资源

用于频率较高,扇出数目较多的时钟使能信号、高速路径关键信号,一是在约束编辑器的专用约束(Misc)选项卡中指定所选信号使用低抖动延迟资源“Low Skew”。也可以直接在约束文件(UCF)中添加“USELOWSKEWLINES”约束命令:

NET "sum " USELOWSKEWLINES;

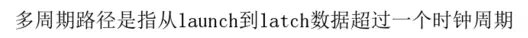

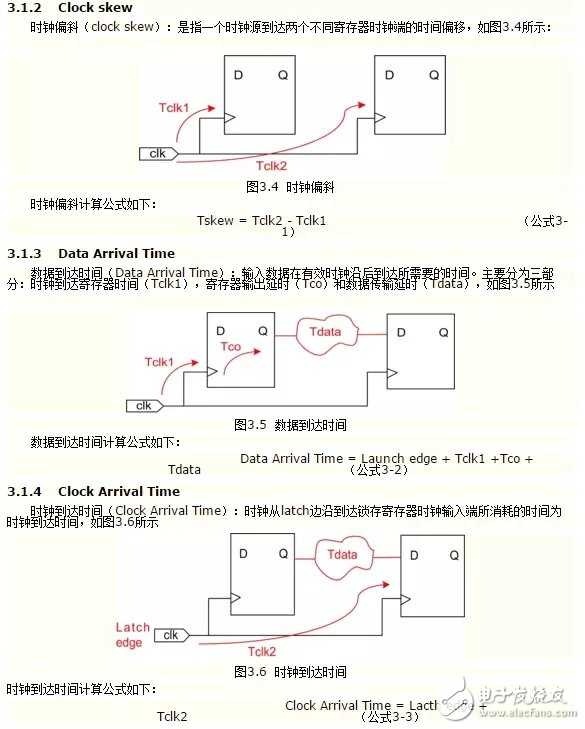

三、静态时序分析

launch edge、latch edge、Tsu、Th、Tco:发射沿、锁存沿、建立、保持、数据输出延时(Tco):这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。

四、时序约束

(1)周期约束

TIMESPEC “TS_identifier” = PERIOD “TNM_reference” {周期长度} {HIGH|LOW} [脉冲持续时间];

TIMESPEC “TS_identifier2” = PERIOD ”timegroup_name” “TS_identifier1” [* | /] 倍数因子 [+|-] phase_value[单位];

TS属性定义,可以用在任意的引用。在使用时要先定义时钟分组,再添加相应的约束,例如:

NET "clk_1" TNM_NET ="clk_syn";

TIMESPEC "TS_clk_syn" = PERIOD "clk_syn" 5ns;

NET "clk_2" TNM_NET ="clk_syn_n";

TIMESPEC "TS_clk_syn_n" = PERIOD "clk_syn_n" clk_syn PHASE + 2.5ns;

NET "clk_3" TNM_NET ="clk_syn_m";

TIMESPEC "TS_clk_syn_m" = PERIOD "clk_syn_m" clk_syn /2;

(2)偏移约束

offset= {in|out} "time"[units] {before|after} "clkname" [TIMEGRP groupname];//[]为选填

1 TNM和TNM_NET约束

TNM进行分组不可以穿越IBUF和BUFG,而TNM_NET则可以。TNM_NET约束只能用于网线上,否则被忽略。

{NET|INST|PIN} "object_name(signals_name)" TNM/TNM_NET = predefined_group or "identifier(net_name)";

2 TIMEGRP约束

用于使已有的分组合并,构成新的分组,或用排除的方法构成新的分组。已有的分组包括预定义的分组和用户自己定义产生的分组。

TIMEGRP "newgrp_name" = "grp_name1" "grp_name2";(合并)

TIMEGRP "newgrp_name" = "grp_name1" EXCEPT "grp_name2";(1中去除2之外剩余的所有部分)

定义受时钟沿控制的触发器分组,如RISING或FALLING沿触发的分组。

TIMEGRP "newgrp_name" = RISING/FALLING "grp_name1";

定义受门控信号控制的锁存器分组,如TRANSLO或TRANSHI的电平控制的分组

TIMEGRP "newgrp_name" = TRANSLO/TRANSHI "grp_name1";

3 TPTHRU约束

用于定义一个或一组中间点,以便在其它时序约束定义中来进行标识,我认为有点象电路图中的网络命名。如下

INST FF1 TNM = "start";

INST FF2 TNM = "endpt";

NET “mynet” TPTHRU= “ABC”;

TIMESPEC “TS_path" = FROM "start" THRU "ABC" TO "endpt" 30;

{NET|INST|PIN}“ ob_name” TPSYNC=“ New_part”;

将TPSYNC 约束附加在网线上,则该网线的驱动源为同步点;附加在同步元件的输出管脚上,则同步元件中驱动该管脚的源为同步点;附加在同步元件上,则输出管脚为同步点;附加在同步元件的输入管脚

上,则该引脚被定义成同步点。

(4)局部约束

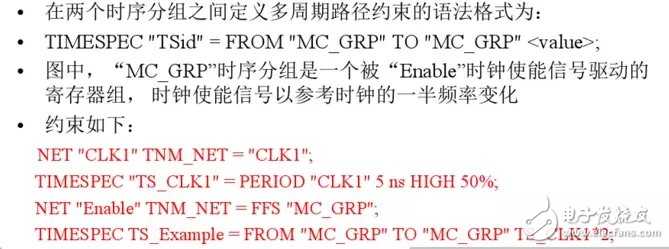

1多周期约束

TIMESPEC “TS_name”= FROM “group1” TO “group2” value; 其中value为延迟时间,可以使具体数值或表达式。

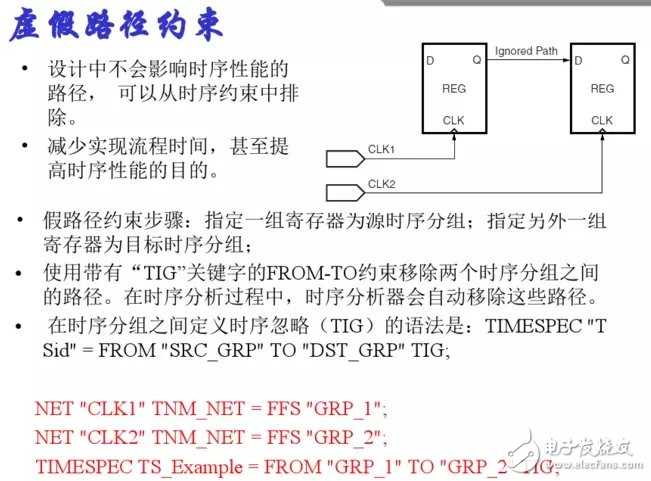

2 虚假路径约束

5.AREA_GROUP 这个暂时还不会用,先写下以后用到再查资料

MAXDELAY约束定义了特定路径上的最大延迟。

语法如下:NET “net_name” MAXDELAY = value units;

艾玛太多了,不想写了,找个全点的资料

谢谢小编的分享 但是图片显示有点问题,小编可否把原贴的地址给我一下,我去将图片补充完好。麻烦小编了~

第一次发不知道还有这回事,我自己能改吗?都是自己整理的,图片没有连接啊~