用FPGA控制ADC芯片,延时应该怎么实现?

时间:10-02

整理:3721RD

点击:

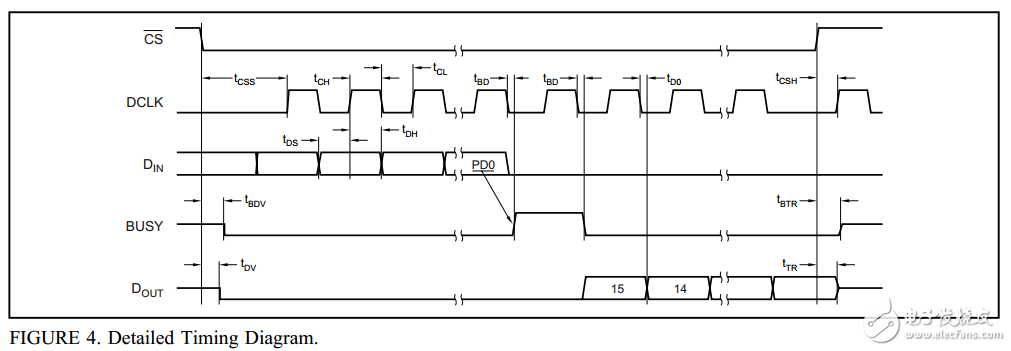

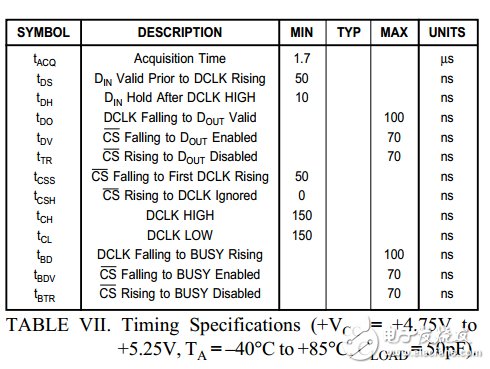

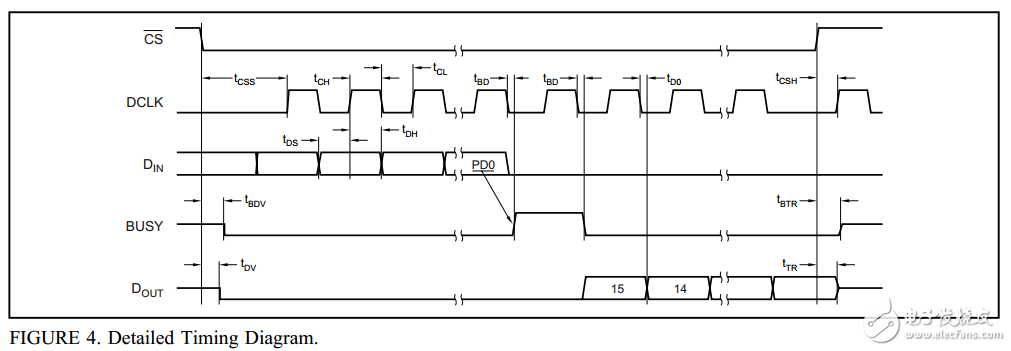

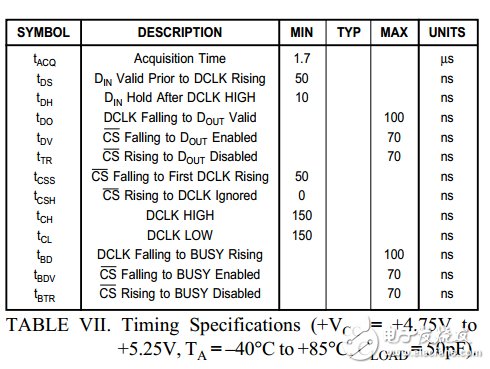

现在要做FPGA控制ADS8344E这个芯片,实现A/D转换。可是看完时序图之后不知道该怎么下手,特别是需要延时的地方,

应该用状态机实现延时还是其他方法?请各位前辈不吝赐教。

应该用状态机实现延时还是其他方法?请各位前辈不吝赐教。

这个时序只是给了一个范围而已,通常时钟给合适,半个时钟周期是可以满足那些时序要求的,不需要严格控制

好文章学习了!谢谢分享

肯定要用状态机的,初步定几个状态,通过时钟或者芯片输出信号来走状态机,就可以实现延时

只要时钟符合,然后再在对计数进行几个延时就ok了,很简单的。

我用VHDL,用case:

process(clk)

begin

if clk'event and clk='1' then

i ce sclk date(0) sclk date(1) ce null;

end case;

end if;