FPGA输入IO漏电流问题

时间:10-02

整理:3721RD

点击:

各位大神好。最近做了块 PCB 板。有个关于输出IO的问题想请教各位。

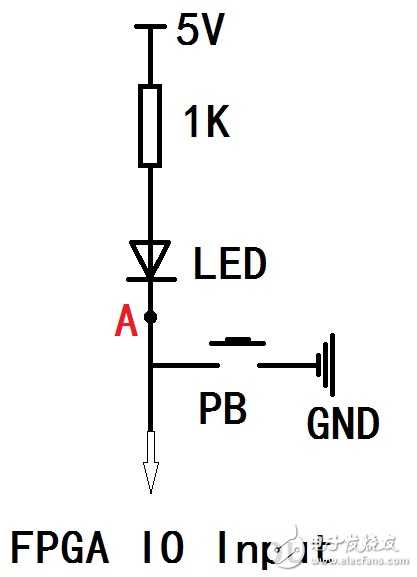

如图片中,5V电源经过一个 1K 电阻与 LED灯。在“A”点电压实测是 3.2V。按键没有按下时,输入是高电平;按键按下时,输入是低电平。

现在有一个问题,是按键没有按下时。LED灯会有微弱的光亮。请问有什么方法设置可以让灯不亮?谢谢

FPGA的电平是3.3V的,你应该把5V的变到3.3V,打赏积分把

谢谢您的回复。

不过电平经过电阻及LED后是有压降的。我实测 “A” 点电压是 3.2V 。

如果把5V换成3.3V,那么“A” 点的电压就只有1.4V左右了。这样不管我按键有没有按下,输入一直都是低电平的。

呵呵,1.4V低电平?你试过

不相信的话,你可以试试。LED上是要有压降的。

LED当然有压降,A点1.4V的话,FPGA认为它是低电平吗?

通过设置IO弱上拉,已解决问题。供参考,谢谢