凔海笔记之FPGA(五):(基本|| 组合)逻辑

时间:10-02

整理:3721RD

点击:

还记得曾写过这样的一句话,任何构造都来源于简单的元件和复杂的逻辑。先作为菜鸟没有那个思维去设计复杂的逻辑,那就说一说见的元件吧\(^o^)/~

一、基本逻辑门电路

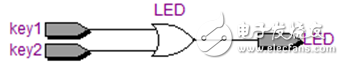

或门电路:有1则为1

assign y = a | b;

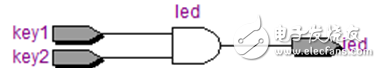

与门电路:有0则为0

与门(英语:AND gate)又称"与电路"、逻辑"积"、逻辑"与"电路。是执行"与"运算的基本逻辑门电路。有多个输入端,一个输出端。当所有的输入同时为高电平(逻辑1)时,输出才为高电平,否则输出为低电平(逻辑0)。

assign led = key1 & key2;

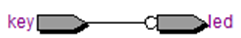

非门:黑白颠倒

非门又称反相器,是逻辑电路的重要基本单元,有输入和输出两个端,输出端的圆圈代表反相的意思

assign led = ~key;

异或:相同为0,不同为1。assign led = key1 ^ key2;

应用:

1、 特定位的翻转;

2、实现俩数值的交换而且不必使用临时变量例如:

例如交换两个整数a=10100001,b=00000110的值,可通过下列语句实现:

a = a^b; //a=10100111

b = b^a; //b=10100001

a = a^b; //a=00000110

2、 置零 a^a

3、 快速判断两个数是否相等:return ((a ^ b) == 0)

4、 加密解密

例如:111^101=010 那加密的过程就是逐个字符跟那个secret字符异或运算.

解密的过程就是密文再跟同一个字符异或运算 010^101=111

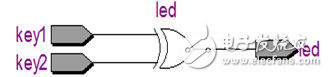

同或门(sor_gate):相同为1,不同为0.

assign led = ~(key1 ^ key2 );

或非门(nor_gate):有0位1 ,全1位0

assign led = ~(key1 | key2);

与非门(nand_gate):有0为1,全1为0.

与非门是与门和非门的结合,先进行与运算,再进行非运算。与运算输入要求有两个,如果输入都用0和1表示的话,那么与运算的结果就是这两个数的乘积。如1和1(两端都有信号),则输出为0;1和0,则输出为1;0和0,这输出为1。

assign led = ~(key1 & key2);

组合逻辑电路

数字逻辑电路分为组合逻辑电路和时序逻辑电路俩大类。对与组合逻辑电路,它在任意时刻产生的输出只取决于该时刻的输入,而与电路的过去的输入无关。

在此,重点介绍数据选择器、编码器、译码器,以便熟悉Verilog的组合逻辑编程。

一、数据选择器

何为数据选择器,顾名思义,就是选择数据的器件,再进一步讲,就是选择输出数据的器件。即在地址选择信号的控制下,从多路输入数据中选择某一路数据作为输出,也称多路选择器或多路开关。常用的芯片有74HC153、74HC151

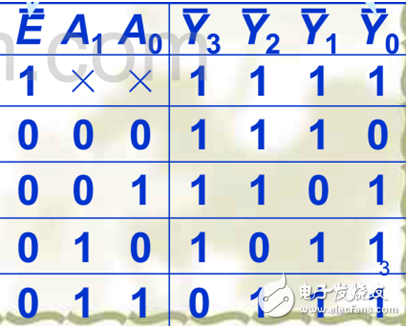

先看一个四选一的数据选择器真值表,即74HC153

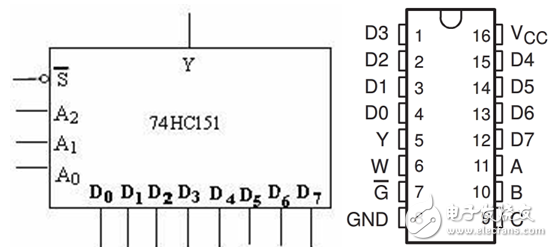

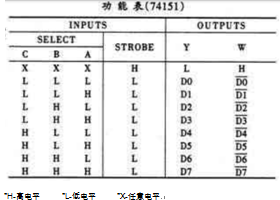

那么,接下来,咱们就以74H151(八选一)为例,用Verilog语言来描述一下。

如下为正值表

*H-高电平 *L-低电平 *X-任意电平

设计方案:

由真值表可知,我们可以用Verilog语言来描述一下74H151。设EN、A、B、C、分别为使能端、输出数据选择端。再令D0~D7为八个事件,而这八个是事件处理结果由A、B、C控制选择输出。加入D0是进行的加法运算,就可以由Y输出连续的0/1代码。现定义D0至D7为七个常量,由A、B、C选择一端输出值Y、Y~。当en为低电平是,Y为高电平,Y~为低电平。

代码见mux8_1。

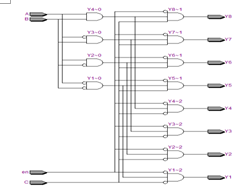

综合的RTL如下

二、8线—3线优先编码器

何为编码器?百度云:“编码是信息从一种形式或格式转换为另一种形式的过程也称为计算机编程语言的代码简称编码。”《数电》云:“用一个二进制代码表示特定含义的信息称为编码。具有编码功能的逻辑电路称为编码器”。说白了,就是

接下来就以优先编码器CD4532为例,用Verilog将其描述。

且看笔者绘制的萌的芯片的功能表。

*H-高电平 *L-低电平 *X-任意电平

从功能表可以看出,该编码器有8个信号输入端,3个二进制码输出端,输入和输出均以高电平为有效电平,而且输出优先级的次序一次为I7、I6……I0。此外,为便于多个芯片连接起来扩展电路的功能,还设置了高电平有效的输入端使能端EI和输出端使能E0,以及优先级编码工作状态GS。

当E1 = 1时,编码工作;而当E1=0时,禁止编码器工作,此时不论8个输入端为何种状态,3个输出端均为低电平,且GS和E0均为低电平。

E0只有在E1为1,且所有输出端都为0时,输出为1,它可以与另一个相同器件的E1连接,以便组成更多输入端的优先级编码器。

GS的功能是,当E1为1,且至少有一个输入端有高电平信号输入时,GS为1,表明编码器处于工作状态,否则GS为0,由此可以区分当电路所有输入端均无高电平输入,或者只有I0输入端有高电平时,Y2Y1Y0均为000的情况。

如何来写代码呢?

首先定义EN为使能端,高电平有效。I1到I7为输入端,假设为八个拨码开关,[2:0]led为输出的三种状态,由输入数据控制。并且设计优先编码,从I1到I7优先级依次降低。

代码参见coder

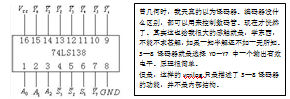

三、3线—8线译码器

译码是编码的逆过程,它的功能是将具有特定含义的二进制码转换成对应的输出信号,完成这种功能的电路称为码转换电路,它包括译码器和编码器。

这里就介绍一种唯一地址译码器,将一系列代码转换成与之一一对应的有效信号。它常用语计算机中对存储器单元地址的译码,即将每一个地址代码转换成一个有效信号,从而选中对应的单元。

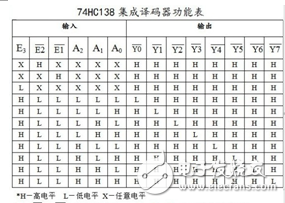

且看真值表:

在看真值表的时候,要注意,对应编码致低电平。其他的为高电平,所以不能再直至不管了。

代码参见3_decoder。

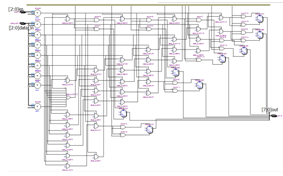

综合的RTL

参见上面两个RTL图可以发现,代码思想很重要呀。

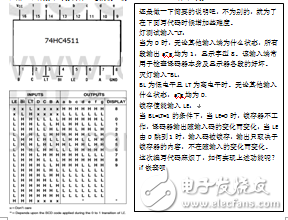

四、BCD—7段译码器

其实这还是一种译码器,只不过是有了它特定的功能而已。而不是根据一种情况输出一个高或低电平。7段译码器就是为了驱动七段式数字显示器而生的。它分输出高电平有效译码器和低电平有效译码器俩种。咱就说一说74HC4511这一种译码器吧。

学识浅薄出拙文,如察错误望赐教,小弟在此感涕零。

欲瞧凔海笔记之单片机、FPGA等系列文章,请戳下面链接(*^__^*) 嘻嘻……

凔海笔记