用VHDL写了一个半加器,Testbench不能出波形

时间:10-02

整理:3721RD

点击:

用VHDL写了一个半加器,利用quartus ii产生的Testbench模板,然后在模板上添加代码,程序在编译能通过,然后在Modelsim里仿真运行,就是不能出波形,个人觉得是程序的事,但是就是找不出错误所在,请大家帮忙看看。

以下是半加器源程序:

library ieee;

use ieee.std_logic_1164.all;

entity half_adder is

port(A : in std_logic;

B : in std_logic;

S : out std_logic;

CO: out std_logic

);

end entity half_adder;

architecture bhv of half_adder is

begin

S A,

B => B,

CO => CO,

S => S

);

init : PROCESS

BEGIN

A <= '0' , '1' after 200 ns , '0' after 200 ns ;

WAIT;

END PROCESS init;

always : PROCESS

BEGIN

B <= '0' , '1' after 100 ns , '0' after 200 ns ;

WAIT;

END PROCESS always;

END half_adder_arch;

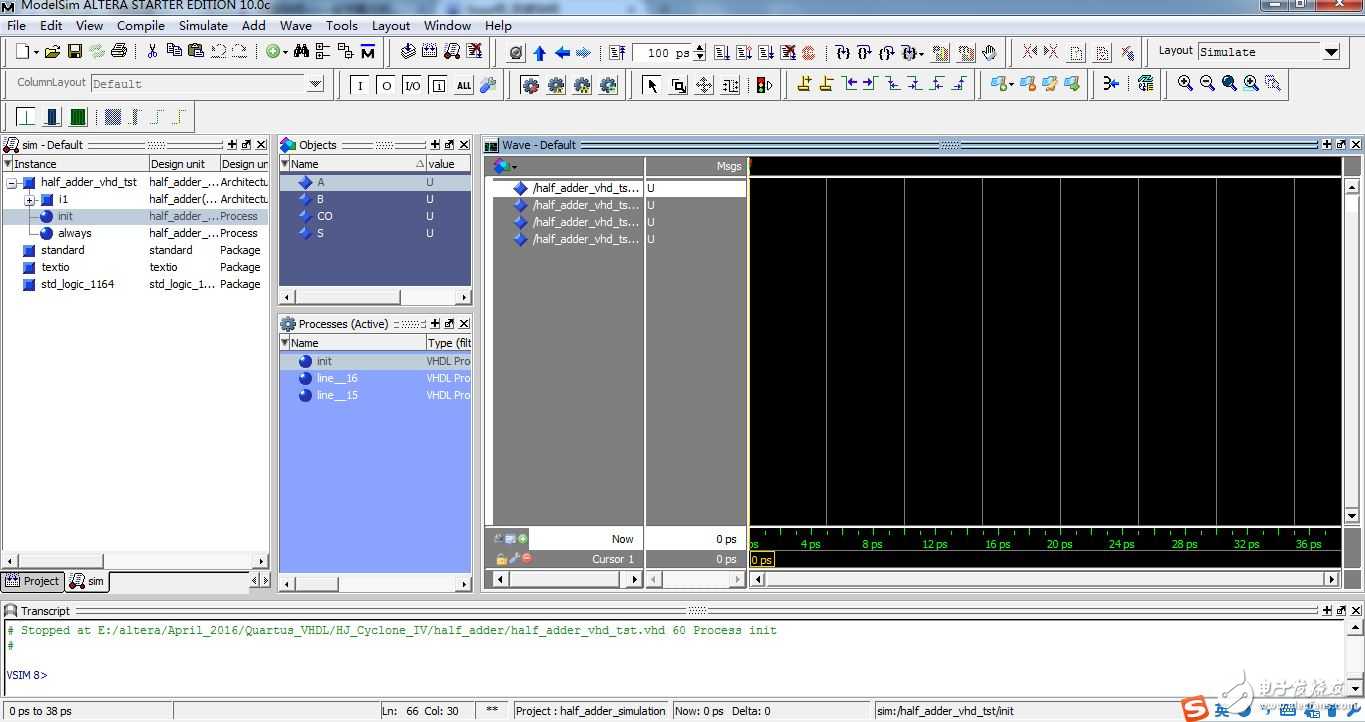

这是运行结果

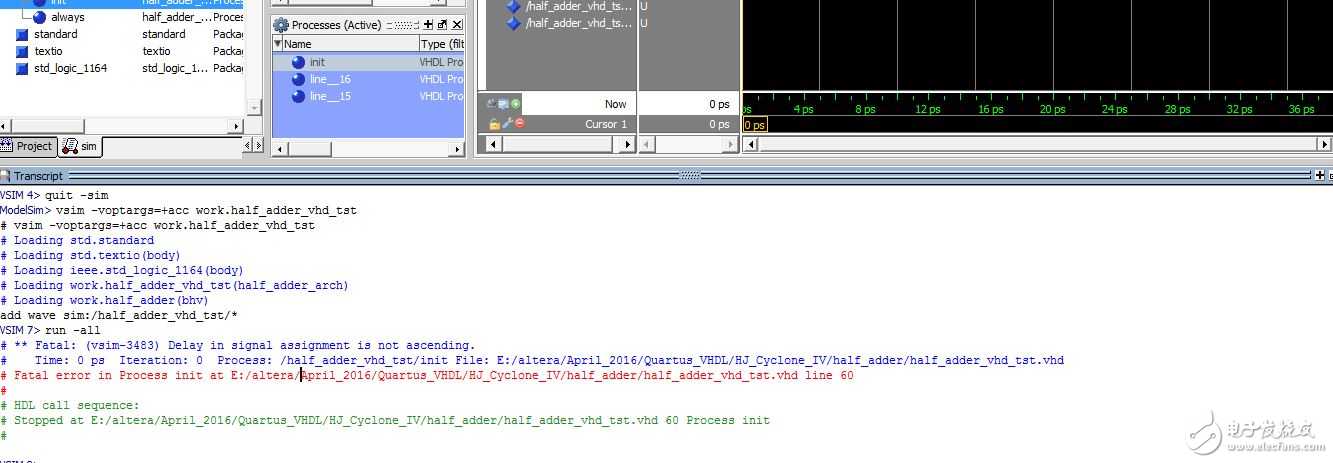

这是错误提示

已退回4积分