凔海笔记之FPGA(连载)

凔海笔记之FPGA(一):我与我的FPGA

“老师,单片机那个试验箱都弄完了,接下来我想学学arm”

“噢,那挺好的,要不你先学学FPGA吧,学好了FPGA再接触arm会学得更好些”

“FPGA?!老师我还不清楚它是干啥的了?也和单片机一样?”

“还不一样,FPGA就像一张白纸,你可以在上面定制你想要的电路。”

“哦,这样啊”

从此,跳入了学FPGA这个大坑。

By the way.我总是感觉老师把我忽悠了。arm和FPGA没一毛钱关系呀?!网上也总是问学arm和FPGA哪个好,或是先学STM32再学arm,还真没听过FPGA与arm还有承接关系。不知可否有高人指点,解我上述疑惑?

不过作为真逗比假文艺的工科男,总会有好的想法来安慰自己。其实这些都是相同的,学好一种便会触类旁通。FPGA是根据需求定制电路,在写接口或是模块时会对一些设计思想或是说接口协议更为了解,百丈高楼平地起,学好FPGA就给这百丈高楼打好了更为坚实的根基。

记得刚接触FPGA时候,那真是同学少年,意气风发,看俩天天特权资料,懂了点Verilog语法,搞明白了下载方式、学会了编程软件、点亮了一个灯。紧接着,打印代码条条分析,观察现象一丝不苟。看懂了兴奋不已,有现象了志得意满,原本以为自己在大步前进,殊不知是原地打转。

在我看来,学习不能刨根问底,对于我等菜鸟来说这只会让自己困恼不已,裹足不前,但也不能浅尝辄止,似懂非懂,这学得越多越会心虚。‘

记得有好多人对我说,代码会改就好,芯片会用就好。搞什么原理结构,做什么代码分析,都是对时间的浪费,做出东西才是最重要的。但慢慢的我觉得,听懂不等于掌握,看懂不等于会写,大学时间充裕,或更应该静心潜学,而不是到处参加竞赛,拿着copy的代码,不懂的原理去美其名曰我的制作,这如同浮沙上的高台,空中的楼阁,积累经验名不属实,厚积薄发更是妄想。

不知当初,是不是被老师忽悠来的,但要感谢老师把我领上道,让我明白了很多,学到了不少。在这里,写下凔海笔记之FPGA系列文章,记录下我与FPGA的美妙旅程。

欲瞧凔海笔记之单片机、FPGA等系列文章,请戳下面链接(*^__^*) 嘻嘻……

凔海笔记

始于足下……

哈哈

以我现在的水平来说FPGA内部结构,那简直就是管中窥豹,盲人摸象,螳臂挡车,猪鼻子插大蒜,总之,定会献丑与众,贻笑大方。

知乎说:“FPGA是现场可编程们阵列,基于硬件描述语言,半定制设计电路”。

老师言:“它就好比一张白纸,你可以在上面描述出自己想要的电路”

可是,它到底是什么呢?

在我看来,任何构造都来源于简单的元件和复杂的逻辑,FPGA就是用简单的元件搭建出复杂的操作平台,让我们在上面定制自己想要的东西。前人是用一个一个元件去连接构造,而我们是用语言描述。例如我要进行串口通讯,那就Description一个、我想进行滤波,那就写个fir、我想模拟51单片机,那也没问题。所以说,无论是Verilog HDL还是VHDL,其中最能体现其特点的就是D(Description)。

我是从单片机转到FPGA的,所以总想对比二者区别以便更好了解。

单片机写程序是为了实现某种控制,我们把写好的程序下载到单片机的程序存储器中,然后一条条的执行,而FPGA是把所写的程序翻译成电路,从而构造出自己想要的电路。例如串口通讯,单片机已有该模块,我们的工作是开启并选择模式,而FPGA需要你描述uart的波特率,如何接收字节发送字节,这一切FPGA里面是没有的,是我们描绘出来的。

曾想到一个例子来理解FPGA。假设有一张神奇桌子,它如同哆啦a梦的四次元口袋,里面有你想要的各种食材、调味品还有饮料和酒,量是一定的但可以重复使用。而你是世界级的厨师,假设完毕。

今天心情格外的好,所以你要做这样的一桌饭。

这和FPGA有何关系呢?下面就要进行映射啦。

桌子就好比是FPGA,那桌子上食材就好比FPGA里面的资源,厨房如同开发软件,一道道菜就是一个一个模块,这一道道菜是独立的但他们也是关联的,因为他们构成这个满汉全席一份子,而满汉全席就是你的杰作。一双双筷子就好比一个个引脚,它完成输出,而且还是并行。人少你可以少做点,人多你可以多做点,但总有一个限度,就是这个神奇桌子里面食材数量的限制。

FPGA(Field-Programmable Gate Array)即现场可编程门阵列。现场可编程是不是就可以认为可以快速定制,也就是说,FPGA是可定制的,所以内部结构构造目的就是为了实现快速构造出所需要的芯片(电路)。而这个电路(芯片)是用编程的方式实现的。之所以能用编程方式而所谓的编程就是写下代码,由软件将它翻译出来,下载到FPGA。

所谓的翻译出来,就是软件把你写的代码翻译成01,如同灌溉农田一样关闭一些通道,打开一些通道,以实现你的目的。为此,FPGA采用了大量的查找表(LUT)、数据选择器和触发器来实现。具体怎么实现,下节聊

学识浅薄出拙文,如察错误望赐教,小弟在此感涕零。

欲瞧凔海笔记之单片机、FPGA等系列文章,请戳下面链接(*^__^*) 嘻嘻……

凔海笔记

这是缘分吧哈哈

支持一下!

搞了两年FPGA,看着ARM在智能领域所向披靡,CPU和ARM都是串行的,FPGA的并行像是剑走偏锋一样。

果然是真逗比假文艺的工科男,哈哈

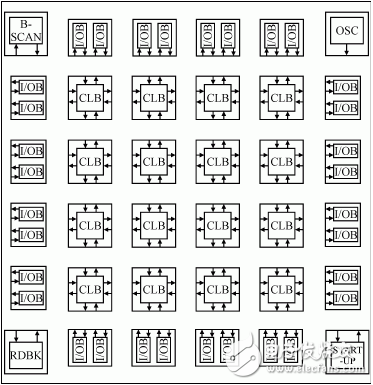

FPGA就好像一个平台,用简单的器件和复杂的逻辑构建起来的。这个平台大概由六部分组成,分别为基本可编程逻辑模块(CLB)、可编程输入/输出模块(IOB)、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。对于不同型号的芯片,其内部结构也会有些变化,但原理都也差不多,所以咱不必在意说的是何种芯片,下面就以鄙陋只见说芯片之精妙。

逻辑块(Logic Block),Altera称之为逻辑阵列块(LAB),Xilinx称之为可配置逻辑课(CLB),我更喜欢CLB这个称呼,因为它说得够清楚,虽然我用的是Altera公司的芯片吧(*^__^*) 。我们所说的Verilog编程,可以说就是对CLB的配置,它可以实现绝大多数的逻辑功能。

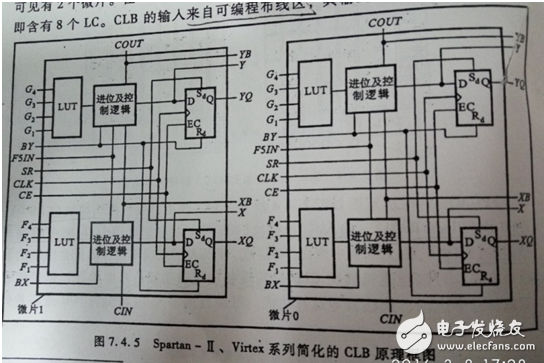

其中LUT(Look-Up Table)即查找表,它的本质是一个16X1的SRAM,SRAM是英文Static RAM的缩写,即静态随机存储器。我们可以认为SRAM是这个东西

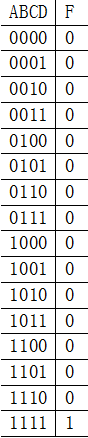

我们通过Verilog语言可以写出逻辑电路,例如F=A&B&C&D,FPGA开发软件会自动计算逻辑电路的所有可能,并把结果放入SRAM,这一过程就是所谓的编程。就那F=A&B&C&D来说,ABCD的组合共有十六组,如下表

当我们下载的时候,软件会自动把上述表格的值送给SRAM,我们ABCD取不同值时,LUT就根据地址进行找到数输出。也就是说,FPGA并不知道我们进行了F=A&B&C&D这一计算,它只是根据我们的输入进行寻址。把LUT与数据选择器配合使用,就可以实现组合逻辑功能,当与触发器结合就可以实现时序逻辑电路的基本功能。

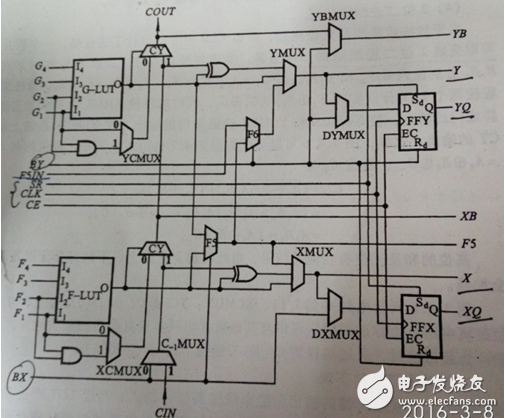

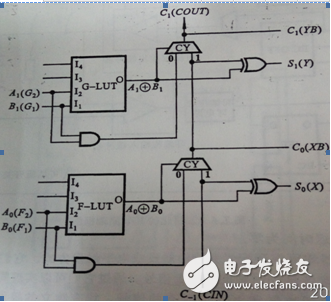

图中除了数据选择器F5、CY、F6外都是可编程的。微片有15个输入端和8个输出端。

15个输入端包括俩组LUT、SR触发器控制端,CLK时钟信号输入端,CE时钟使能控制端。F5IN级联输入端,BX、BY旁路输入端、CIN进位链输入端

8个输出包括2个组合逻辑输出端X和Y,2个寄存器输出端XQ和YQ,2个算数运算进位端BX和BY,1个级联输出端F5和1个进位链输出端COUT。

在我第一次看这些名词时,真是怀疑自己的智商了。

可是,不看不行呀/(ㄒoㄒ)/~~所以先接单的说一下各器件吧

LUT不废话,过

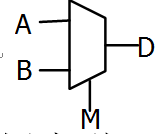

数据选择器:

与门:

异或:

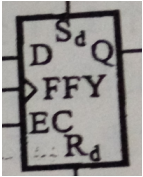

触发器:

实现时序逻辑就是因为这个,D数据输入,FFY时钟信号输入,它来一拍,数据传输一个。EC时钟使能,Sd触发器控制,Rd复位控制。

下面就通过举例来说一下各种功能

(1)实现4变量的任意逻辑函数。

例如要实现F=A^B&C||D。那么就如上表格方式计算出所有的可能,将ABCD依次送给F1~F4,O端得到4变量逻辑函数的结果。该结果可以经过XMUX直接从X输出,也可以经DCMUX和D触发器由XQ输出。

(2)实现5变量的任意逻辑函数

5变量?!那一个LUT肯定是不够了。F=A^B&C||D&E肿么办?这时BX成了救世主,我们把ABCD这四个数据时同时送到送入F1~F4以及G1~G4的同时,将第五个数E送给BX。Why?Σ( ° △ °|||)︴因为五个数有32种可能,一个LUT只能存储16种,这样俩个就存储32种啦。而且,如果我们在G-LUT中放的是ABCD任意值,而E为1,在F-LUT中放的也是ABCD任意值,但E=0。这时候第五个变量的输入就起到选择这俩个LUT哪个输出!

真的太巧妙了。

有了5变量的基础,实现六变量就好理解了,六变量逻辑函数需要俩个微片。因为由2^6=64嘛。我们假设要实现W=A^B&C||D&E&F。则可以让微片一号的G-LUT存放地址ABCD任意值E=0,F=1,F-LUT存放ABCD任意值E=1,F=1。E从BX输入。微片二号G-LUT存放地址ABCD任意值E=0,F=0,F-LUT存放ABCD任意值E=1,F=0。E从BX输入,F从BY输入。微片一号从F5输出值接到微片二号的F5IN即可完成。结果可经过YMUX从Y输出,可再经DYBMUX由触发器输出。

(4)2位二进制加法器

就这个微片,小小的微片,愣生生的“山寨”了小俩千字,真佩服设计者的智慧,如果将此看做一件艺术品的话,我想匠心独运名副其实。

山寨源:

[1]度娘友情提供

[2]康华光老师主编的电子技术基础数字部分(第五版)全程赞助

(未完待续)

欲瞧凔海笔记之单片机、FPGA等系列文章,请戳下面链接(*^__^*) 嘻嘻……

凔海笔记

嘿嘿,那是嘛

小编总结很好 跟帖

"大学时间充裕,或更应该静心潜学,而不是到处参加竞赛,拿着copy的代码,不懂的原理去美其名曰我的制作,这如同浮沙上的高台,空中的楼阁,积累经验名不属实,厚积薄发更是妄想。"

你将来能在这行走多远、爬多高,全看你大学时期基础有多牢靠!

支持支持

期待更新,期待开讲堂

同样,我也是导师领上道了,下不来了,哈哈!记得学数电时,对可编程逻辑阵列印象深刻,这是个大趋势,没想到,altera被intel收购,芯片大佬都意识到的问题,我们还不赶紧跟上!逻辑学精,上内核,爽歪歪!

支持支持支持支持

代码会改就好,芯片会用就好。搞什么原理结构,做什么代码分析,都是对时间的浪费,做出东西才是最重要的。

比赛的时候 老师也是这么说的,。

诶,FPGA挺好的,就是成本高太多,应用太少,岗位也太少。

小编所言犹如醍醐灌顶,受教了。

加油↖(^ω^)↗

谢谢支持,如有错误,还请不吝赐教

我们老师也说过类似的话,那你认同不?

一起学习,如有错误,还请不吝赐教呀

学习 好文章 值得一看

文章写的很具吸引力,加油写!我继续往下看