FPGA中实现PID算法

在FPGA中实现PID算法,面临着小数的计算,请问大家一般是怎么处理的?

温度控制是用单闭环的PID算法控制。

无刷电机控制是用双闭环PI算法,也就是在电机控制里经常提到的电流环和速度环。

最近抽空初步完成了PID算法的FPGA实现。

增量式的PID控制理论,这里就不说了,博客里有具体公式。

整个算法过程说直白点就是公式的硬件实现,用到了altera提供的IP核,整个的设计要注意的时钟的选

取,流水线的应用

回答好棒,赞一个

能不能不要这样。

小编有用FPGA实现pid控制的程序吗?跪求。

可以先扩大,再缩小

FPGA好像不太支持浮点数,先扩大N倍,算出结果再统一缩小。

能不能参考一下

能有程序参考一下最好

小数点,是你先要规定的,比如一个32bit的数据,你可以规定有 多少bit是整数,多少bit是小数。运算的时候,先把该32bit的数乘以2的小数位数次方,全部搞成整数,整数算完活,自己再做缩小处理,或者是把其它量也一起放大,都放在整数处理。

先左移,相乘之后再右移,取整数部分,小数部分舍去

这个方法我知道,但是我觉得实行起来是不是有误差,而且左移相当于*2^N,那么对于任意数而言,有些根本不能通过左移取得整数,这时候就必须舍去小数部分,经过运算之后再右移。不知道实际用的怎么样。

这个有木有什么范例程序供参考一下。程序分析我觉得更具体些。

其实可以有DSP和ARM核之类的,(1)有浮点的核,官方自带的;(2)嵌入nios,就可以算浮点了;(3)自己写浮点核;(4)用嵌入arm的高端FPGA。但是我们现在就单纯的争对FPGA做简单的浮点数运算。

能不能把你的成果给我们讲解一下呢

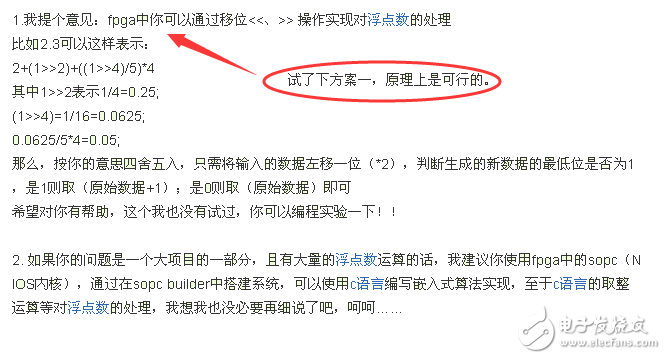

(转)FPGA中浮点数的处理方式:

接16楼:

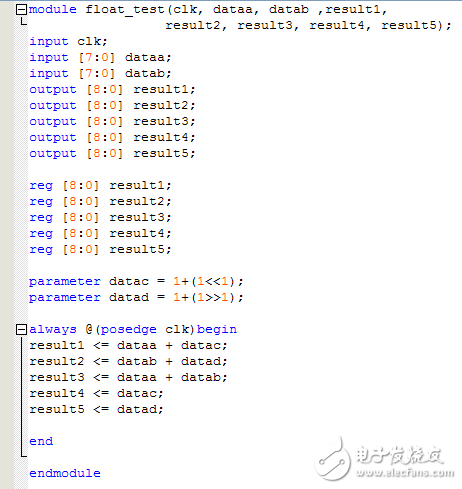

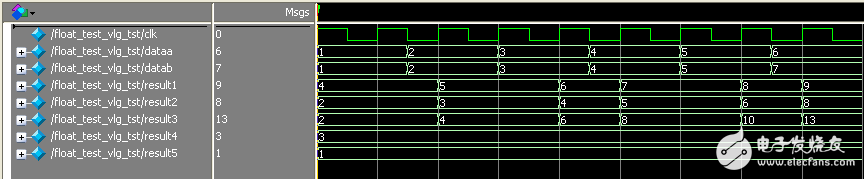

方案一程序以及仿真:(觉得不行)

个人觉得放大2的n次方倍,最后在缩小,比较易于整体操作

大红枣的博客是多少?