在做fpga双口ram的时候 这是我做的仿真 为什么读地址、和写地址计数只能读到7

时间:10-02

整理:3721RD

点击:

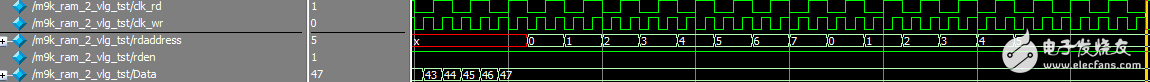

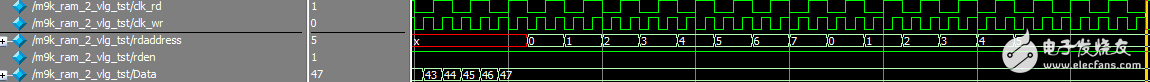

我写的testbench 给 rdaddress的值, 但是仿真出来的 rdaddress的值是 0~7,0~5 这样14位 而不是 0~14看仿真图

// #10 rdaddress = 3'd0;

#15 rdaddress = 3'd0;

#20 rdaddress = 3'd1;

#20 rdaddress = 3'd2;

#20 rdaddress = 3'd3;

#20 rdaddress = 3'd4;

#20 rdaddress = 3'd5;

#20 rdaddress = 3'd6;

#20 rdaddress = 3'd7;

#20 rdaddress = 3'd8;

#20 rdaddress = 3'd9;

#20 rdaddress = 3'd10;

#20 rdaddress = 3'd11;

#20 rdaddress = 3'd12;

#20 rdaddress = 3'd13;

// #10 rdaddress = 3'd0;

#15 rdaddress = 3'd0;

#20 rdaddress = 3'd1;

#20 rdaddress = 3'd2;

#20 rdaddress = 3'd3;

#20 rdaddress = 3'd4;

#20 rdaddress = 3'd5;

#20 rdaddress = 3'd6;

#20 rdaddress = 3'd7;

#20 rdaddress = 3'd8;

#20 rdaddress = 3'd9;

#20 rdaddress = 3'd10;

#20 rdaddress = 3'd11;

#20 rdaddress = 3'd12;

#20 rdaddress = 3'd13;

你把它改成每一个clk_rd的上升沿,rdaddress加一,然后到你需要的时间$stop。

你的rdaddress很可能只定义了3位,明白了吗?2的3次幂等于8,也就说你只能访问0到7。下次别这么马虎了

对啊 我昨天发帖后 也发现这个问题,然后改完,,问题就解决了 。 但是有点不明白 我在testbench 明明定义的是3’d13 那不是应该是3位的10进制吗? 为什么会是定义3位的8进制?

那3位的十进制最多也是7啊,3'b111。

3’d111;不是 十进制111吗 不是7吧?

3位是指硬件上的3位基本逻辑单元,对于逻辑单元来说,只有0与1,所以永远都是2进制。

好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好好

懂了 谢谢