PLL时钟进行时序约束后的相位问题

时间:10-02

整理:3721RD

点击:

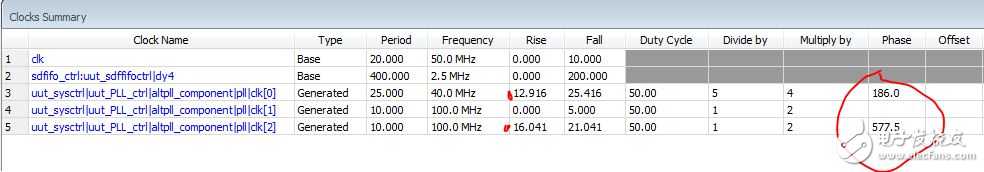

如图所示,clk是源时钟,clk[0],clk[1],clk[2]是PLL的输出时钟,其中clk[0]和clk[2]有延迟,这个问题怎么解决?

setup time slack和hold time slack都没有问题,但我还是想解决它。尝试过让其他时钟延迟,添加了set clock latency,但并没有什么用。所以求高手解决。

你生成pll的时候设置了他们的相位关系吧,你看其他跟源时钟没有延迟的Rise都是0.00ns,才能跟源时钟的相位对齐,现在你这两个时钟的Rise不是0.00ns,所以肯定相对于源时钟有相位变化。你重新生成一次,生成的时候,记得把相位都设成一样的,肯定有选项让你选择的,要么是phase,要么是Rise,两者之一肯定可以设置。

谢了,我试试。